SerDes 知识详解 一、 SerDes 的作用 1

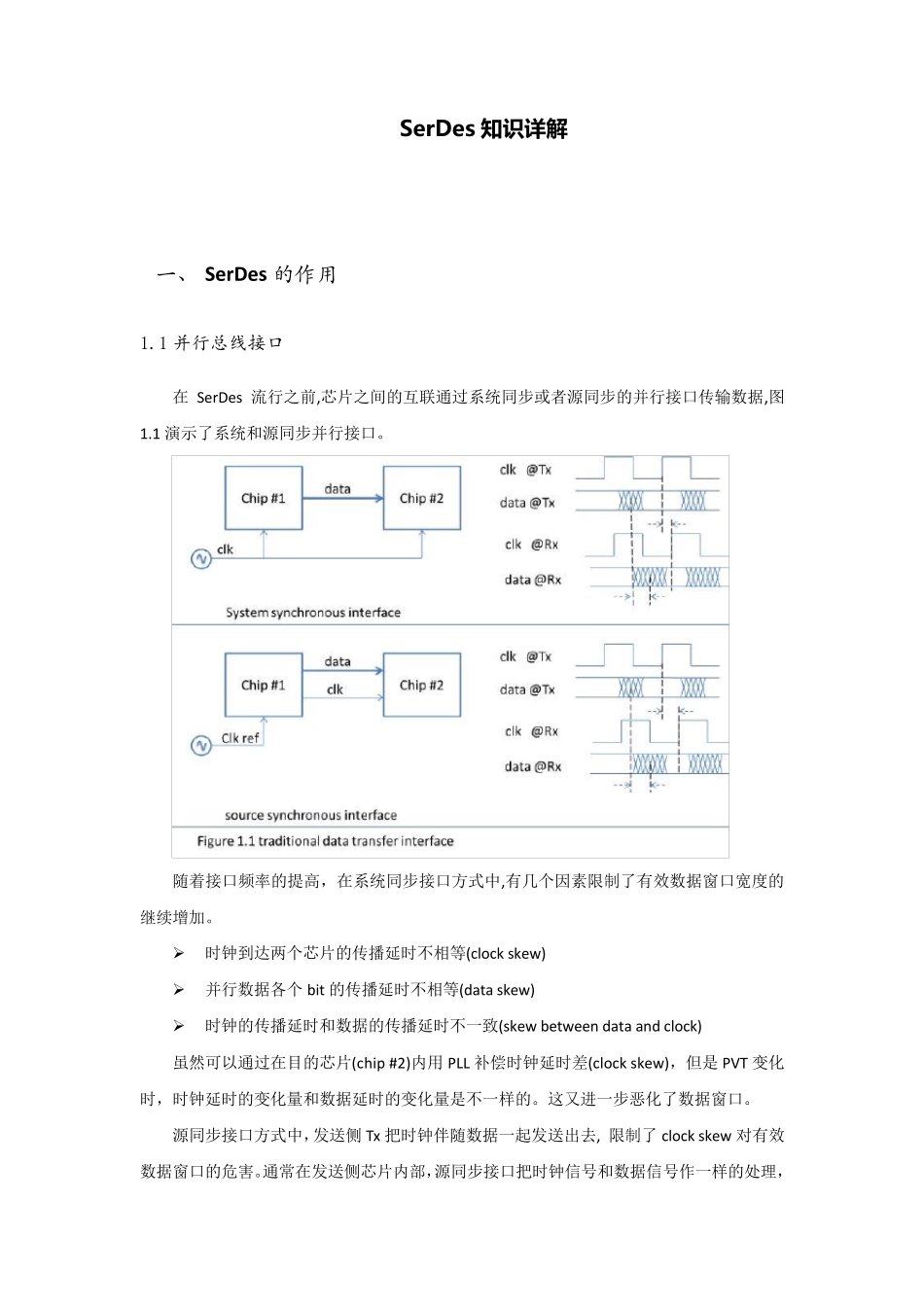

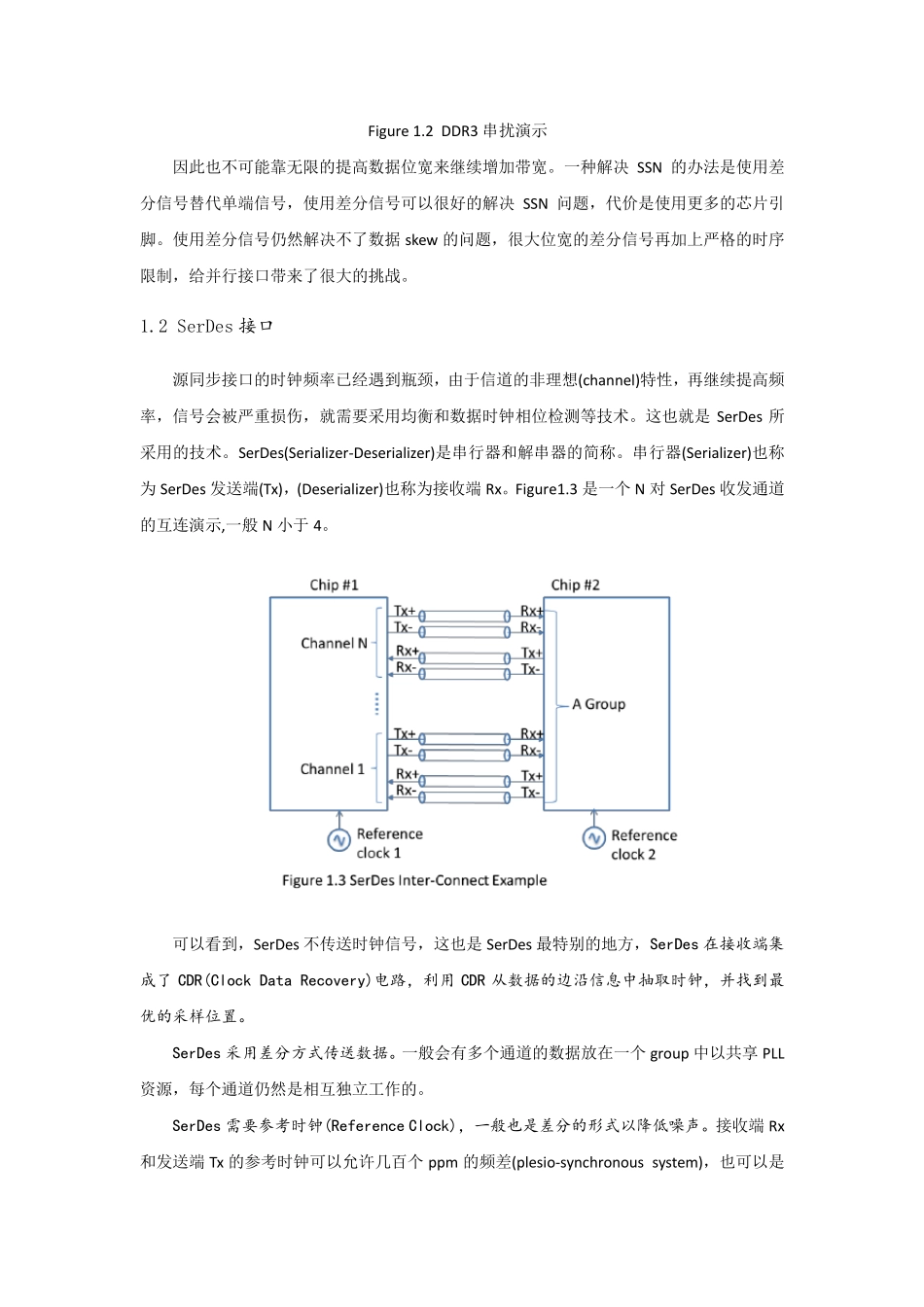

1 并行总线接口 在SerDes 流行之前,芯片之间的互联通过系统同步或者源同步的并行接口传输数据,图1

1 演示了系统和源同步并行接口

随着接口频率的提高,在系统同步接口方式中,有几个因素限制了有效数据窗口宽度的继续增加

➢ 时钟到达两个芯片的传播延时不相等(clock skew) ➢ 并行数据各个 bit 的传播延时不相等(data skew) ➢ 时钟的传播延时和数据的传播延时不一致(skew between data and clock) 虽然可以通过在目的芯片(chip #2)内用 PLL 补偿时钟延时差(clock skew),但是 PVT 变化时,时钟延时的变化量和数据延时的变化量是不一样的

这又进一步恶化了数据窗口

源同步接口方式中,发送侧 Tx把时钟伴随数据一起发送出去, 限制了clock skew 对有效数据窗口的危害

通常在发送侧芯片内部,源同步接口把时钟信号和数据信号作一样的处理, 也就是让它和数据信号经过相同的路径,保持相同的延时

这样 PVT 变化时,时钟和数据会朝着同一个方向增大或者减小相同的量,对 skew 最有利

我们来做一些合理的典型假设,假设一个 32bit 数据的并行总线, a)发送端的数据skew = 50 ps ---很高的要求 b)pcb 走线引入的skew = 50ps ---很高的要求 c)时钟的周期抖动 jitter = +/-50 ps ---很高的要求 d)接收端触发器采样窗口 = 250 ps ---Xilinx V7 高端器件的IO 触发器 可以大致估计出并行接口的最高时钟 = 1/(50+50+100+250) = 2

2GHz (DDR)或者 1

1GHz (SDR)

利用源同步接口,数据的有效窗口可以提高很多

通常频率都在 1GHz 以下