下载后可任意编辑FPGA 流水线概括之前一篇博文(流水线加法器设计(Verilog))介绍了 2 级流水线 4 位全加器,原来目的是和之前不运用流水线的加法器延时进行比较,不过结果程序写得不太好,也被 codeman 大侠指出了错误的地方,于是尝试一下从新改写,于是有了这篇博文

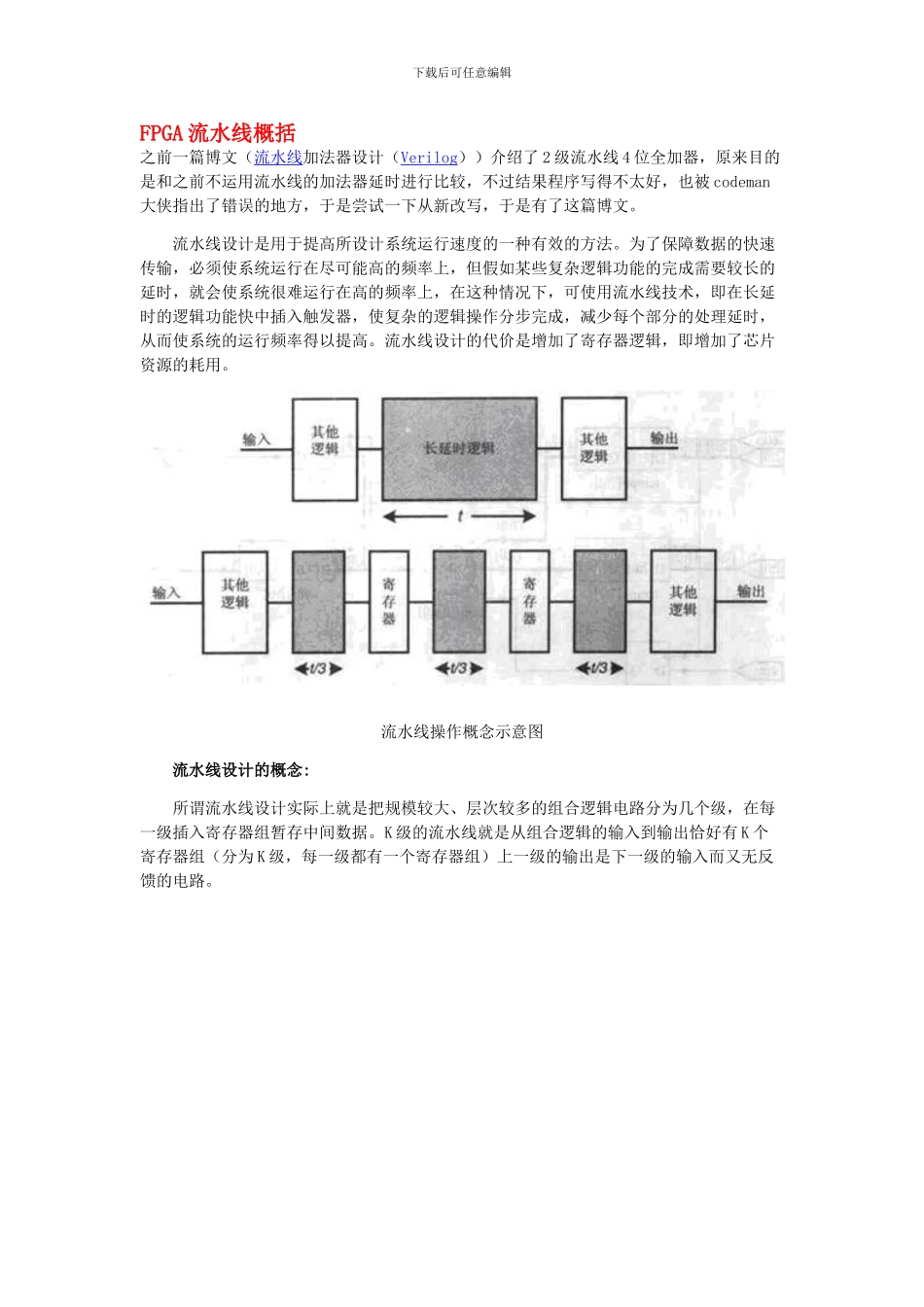

流水线设计是用于提高所设计系统运行速度的一种有效的方法

为了保障数据的快速传输,必须使系统运行在尽可能高的频率上,但假如某些复杂逻辑功能的完成需要较长的延时,就会使系统很难运行在高的频率上,在这种情况下,可使用流水线技术,即在长延时的逻辑功能快中插入触发器,使复杂的逻辑操作分步完成,减少每个部分的处理延时,从而使系统的运行频率得以提高

流水线设计的代价是增加了寄存器逻辑,即增加了芯片资源的耗用

流水线操作概念示意图 流水线设计的概念: 所谓流水线设计实际上就是把规模较大、层次较多的组合逻辑电路分为几个级,在每一级插入寄存器组暂存中间数据

K 级的流水线就是从组合逻辑的输入到输出恰好有 K 个寄存器组(分为 K 级,每一级都有一个寄存器组)上一级的输出是下一级的输入而又无反馈的电路

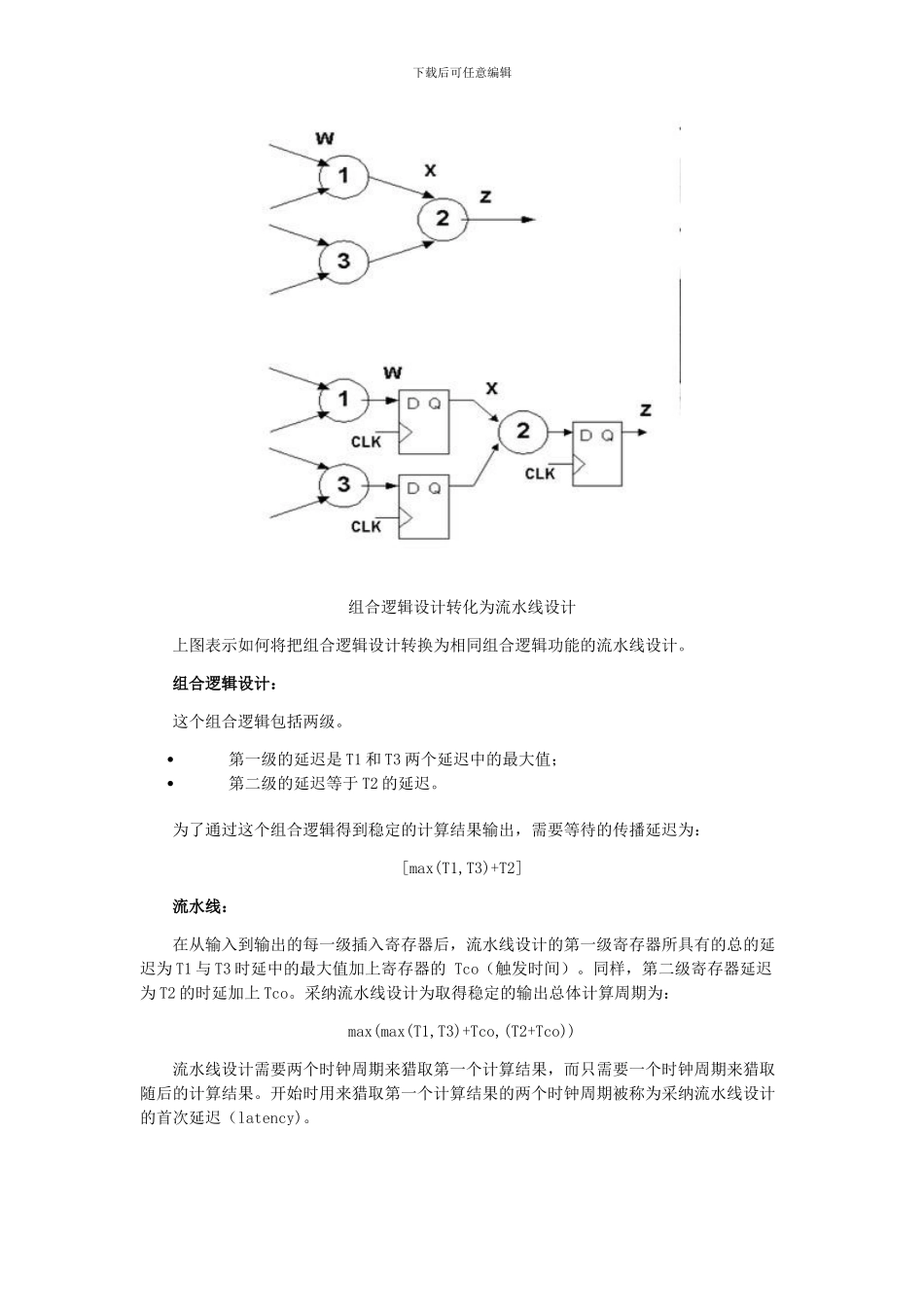

下载后可任意编辑组合逻辑设计转化为流水线设计 上图表示如何将把组合逻辑设计转换为相同组合逻辑功能的流水线设计

组合逻辑设计: 这个组合逻辑包括两级

第一级的延迟是 T1 和 T3 两个延迟中的最大值; 第二级的延迟等于 T2 的延迟

为了通过这个组合逻辑得到稳定的计算结果输出,需要等待的传播延迟为:[max(T1,T3)+T2] 流水线: 在从输入到输出的每一级插入寄存器后,流水线设计的第一级寄存器所具有的总的延迟为 T1 与 T3 时延中的最大值加上寄存器的 Tco(触发时间)

同样,第二级寄存器延迟为 T2 的时延加上 Tco

采纳流水线设计为取得稳定的输出总体计算周期为:max(max(T1,T3)+