1 时钟模块 DCOCTL DCO 控制寄存器 7 6 5 4 3 2 1 0 DCO

4 定义 8 种频率之一,可以分段调节 DCOCLK 频率,相邻两种频率相差10%

而频率由注入直流发生器的电流定义

4 定义在 32 个 DCO 周期中插入的 Fdco+1 周期个数,而在下的 DCO 周期 中为 Fdco 周期,控制改换 DCO 和 DCO+1 选择的两种频率

如果 DCO 常数为 7,表示 已经选择最高频率,此时不能利用 MOD

4 进行频率调整

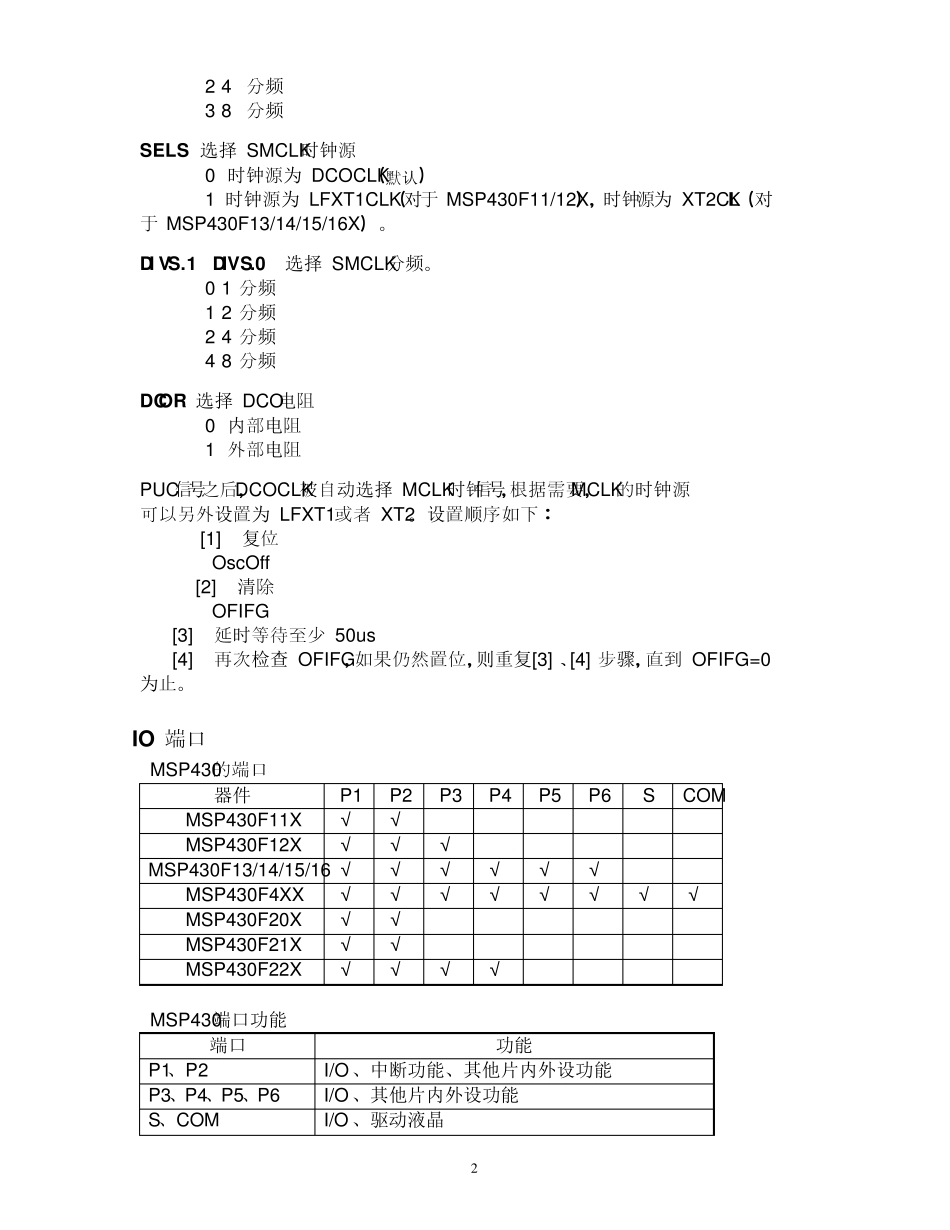

BCSCTL1 基本时钟系统控制寄存器 1 7 6 5 4 3 2 1 0 XT2OFF TXS DIVA

1 DIVA

0 XT5V Rs el

2 Res l

1 Res l

0 XT2OFF 控制 XT2 振荡器的开启与关闭

TX2OFF=0,XT2 振荡器开启

TX2OFF=1,TX2 振荡器关闭(默认为 TX2 关闭) XTS 控制 LFXT1 工作模式,选择需结合实际晶体振荡器连接情况

XTS=0,LFXT1 工作在低频模式(

XTS=1,LFXT1 工作在高频模式(必须连接有高频相应的 DIVA

0 DIVA

1 控制 ACLK 分频

0 不分频(默认) 1 2 分频 2 4 分频 3 8 分频 XT5V 此位设置为 0

0,Resl1

1,Resl1

2 三位控制某个内部电阻以决定标称频率

Resl=0,选择最低的标称频率

Resl=7,选择最高的标称频率

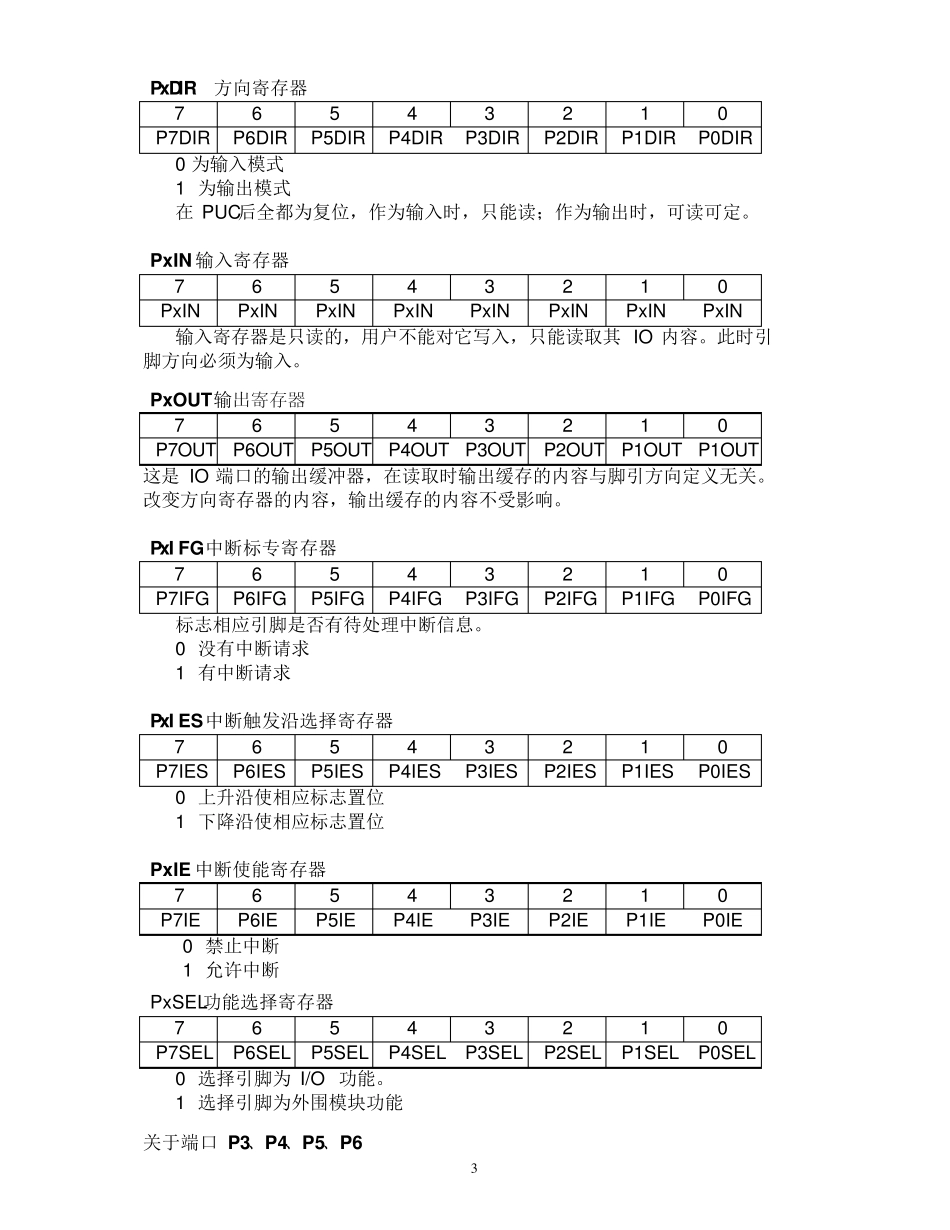

BCSCTL2 基本时钟系统控制寄存器 2 7 6 5 4 3 2 1 0 SELM

1 SELM

0 DIVM

1 DIVM

0 SELS DIVS

1 DIVS