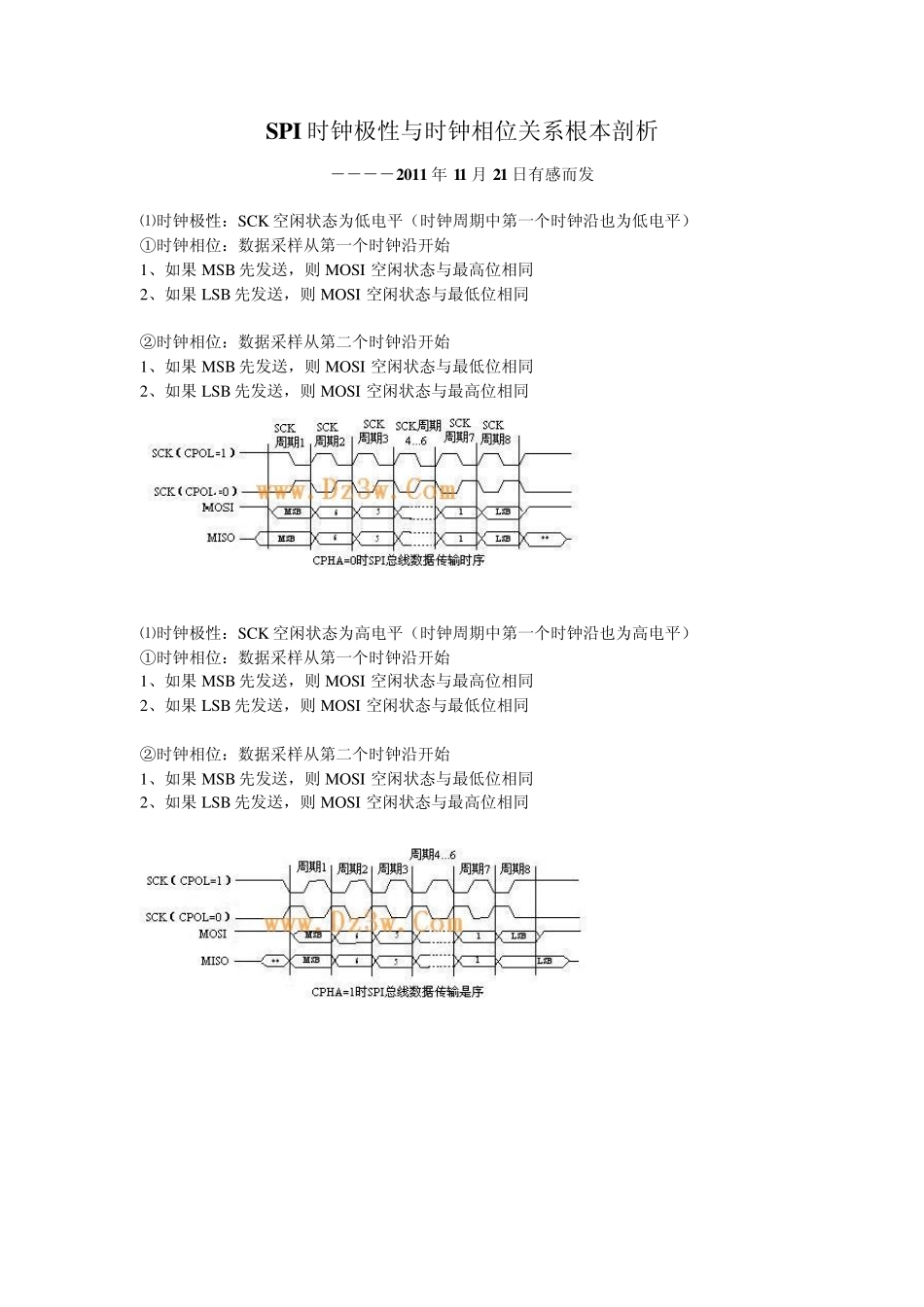

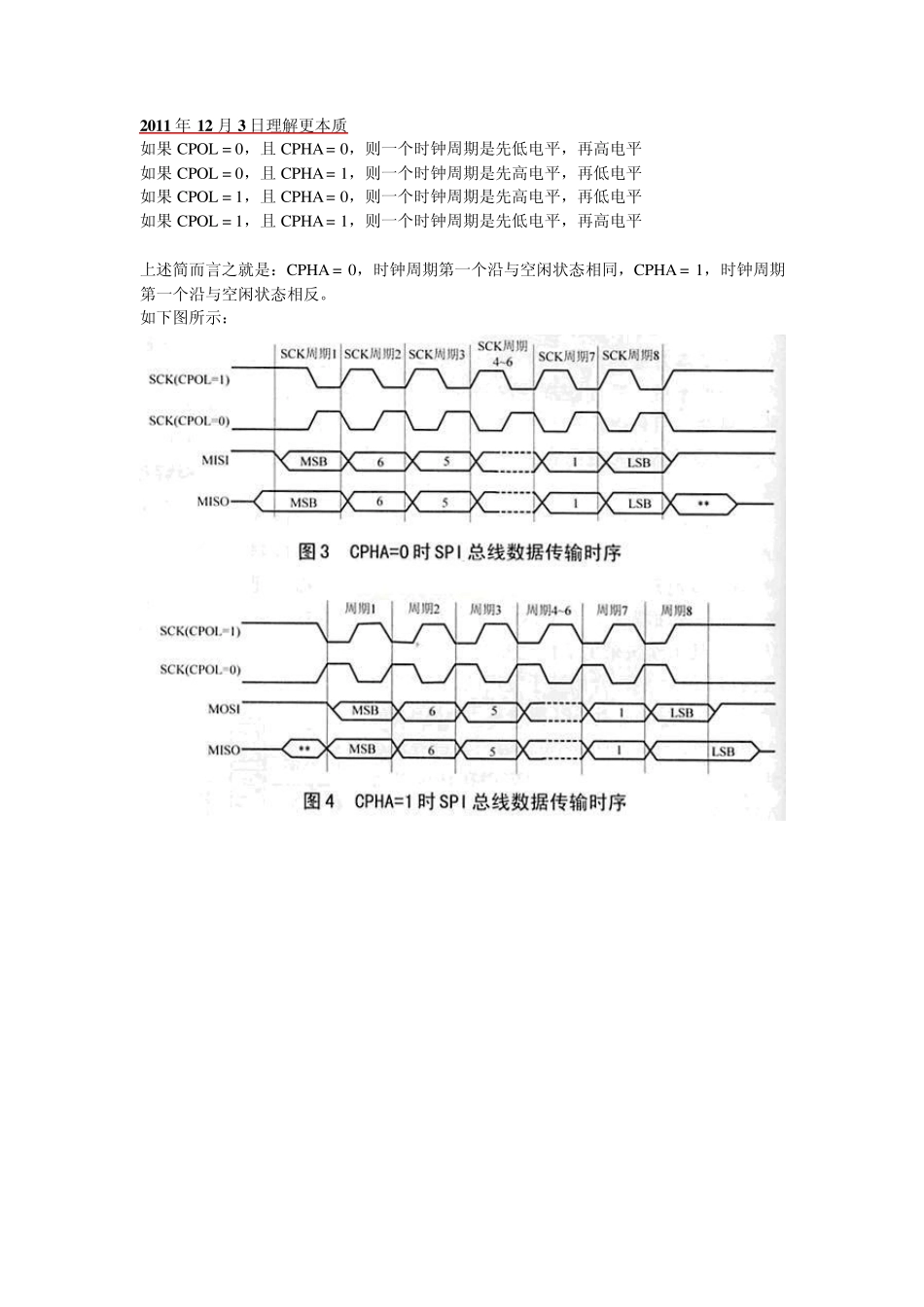

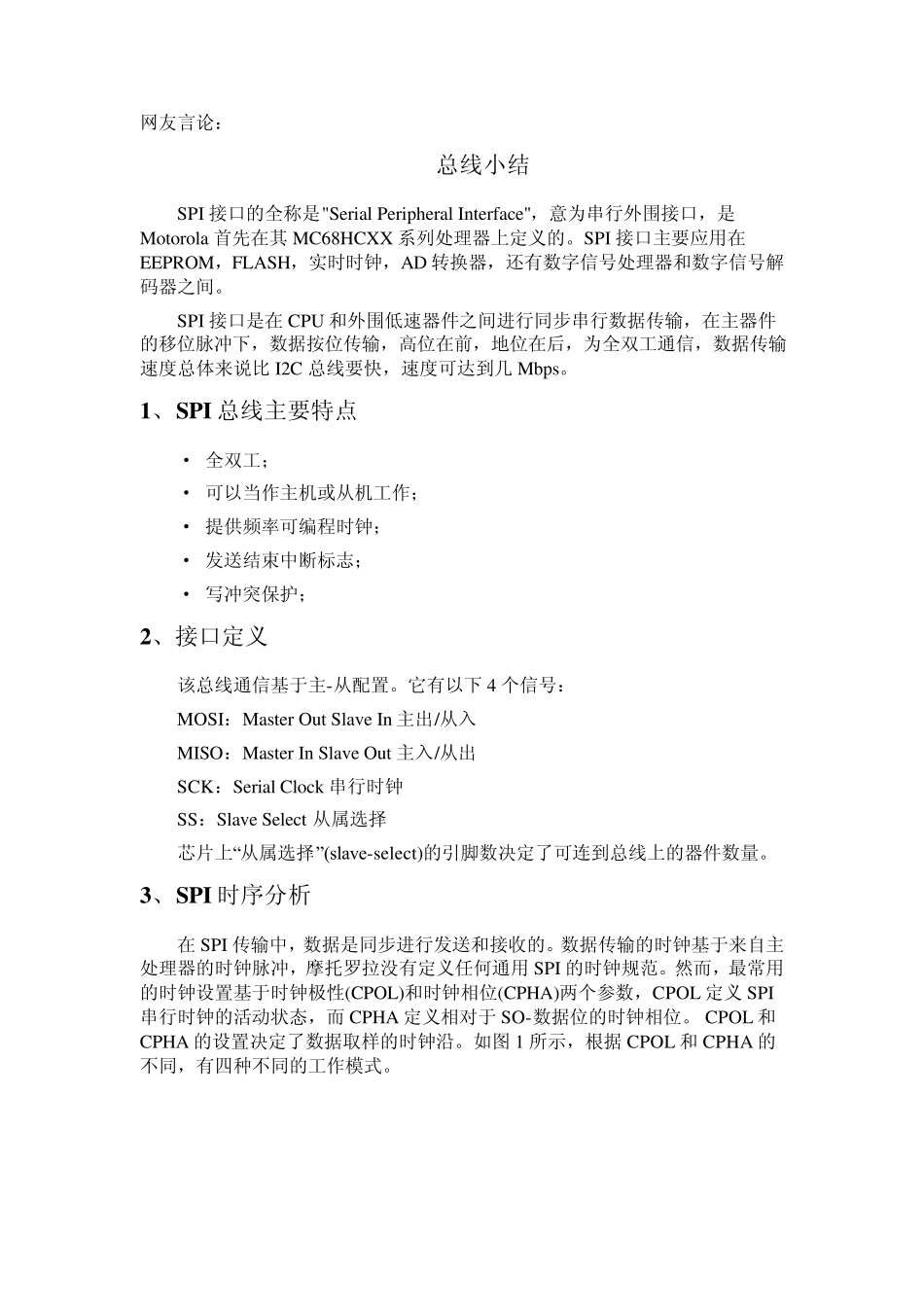

SPI 时钟极性与时钟相位关系根本剖析 ----2011 年11 月21 日有感而发 ⑴时钟极性:SCK 空闲状态为低电平(时钟周期中第一个时钟沿也为低电平) ①时钟相位:数据采样从第一个时钟沿开始 1、如果 MSB 先发送,则 MOSI 空闲状态与最高位相同 2、如果 LSB 先发送,则 MOSI 空闲状态与最低位相同 ②时钟相位:数据采样从第二个时钟沿开始 1、如果 MSB 先发送,则 MOSI 空闲状态与最低位相同 2、如果 LSB 先发送,则 MOSI 空闲状态与最高位相同 ⑴时钟极性:SCK 空闲状态为高电平(时钟周期中第一个时钟沿也为高电平) ①时钟相位:数据采样从第一个时钟沿开始 1、如果 MSB 先发送,则 MOSI 空闲状态与最高位相同 2、如果 LSB 先发送,则 MOSI 空闲状态与最低位相同 ②时钟相位:数据采样从第二个时钟沿开始 1、如果 MSB 先发送,则 MOSI 空闲状态与最低位相同 2、如果 LSB 先发送,则 MOSI 空闲状态与最高位相同 2 0 1 1 年1 2 月3 日理解更本质 如果CPOL = 0,且CPHA = 0,则一个时钟周期是先低电平,再高电平 如果CPOL = 0,且CPHA = 1,则一个时钟周期是先高电平,再低电平 如果CPOL = 1,且CPHA = 0,则一个时钟周期是先高电平,再低电平 如果CPOL = 1,且CPHA = 1,则一个时钟周期是先低电平,再高电平 上述简而言之就是:CPHA = 0,时钟周期第一个沿与空闲状态相同,CPHA = 1,时钟周期第一个沿与空闲状态相反

如下图所示: 网友言论: SPI总线小结 SPI 接口的全称是"Serial Peripheral Interface",意为串行外围接口,是Motorola 首先在其MC68HCXX 系列处理器上定义的

SPI 接口主要应用在EE