STM32 的FSMC 扩展SRAM 的时序测量及配置 STM32 的FSMC 扩展SRAM 的时序测量及配置 目录 1

STM32F103 的FSMC 扩展SRAM 时序介绍及测量 2

STM32F2/F4 的FSMC 扩展SRAM 时序介绍及测量 3

IS61LV25616 高速SRAM 的时序配置 4

EM681FV16AU 中速大容量SRAM 的时序配置 Author: aozima 2012/4/30 STM32 的FSMC 扩展SRAM 的时序测量及配置 1

STM32F103 的FSMC 扩展SRAM 时序介绍及测量 1

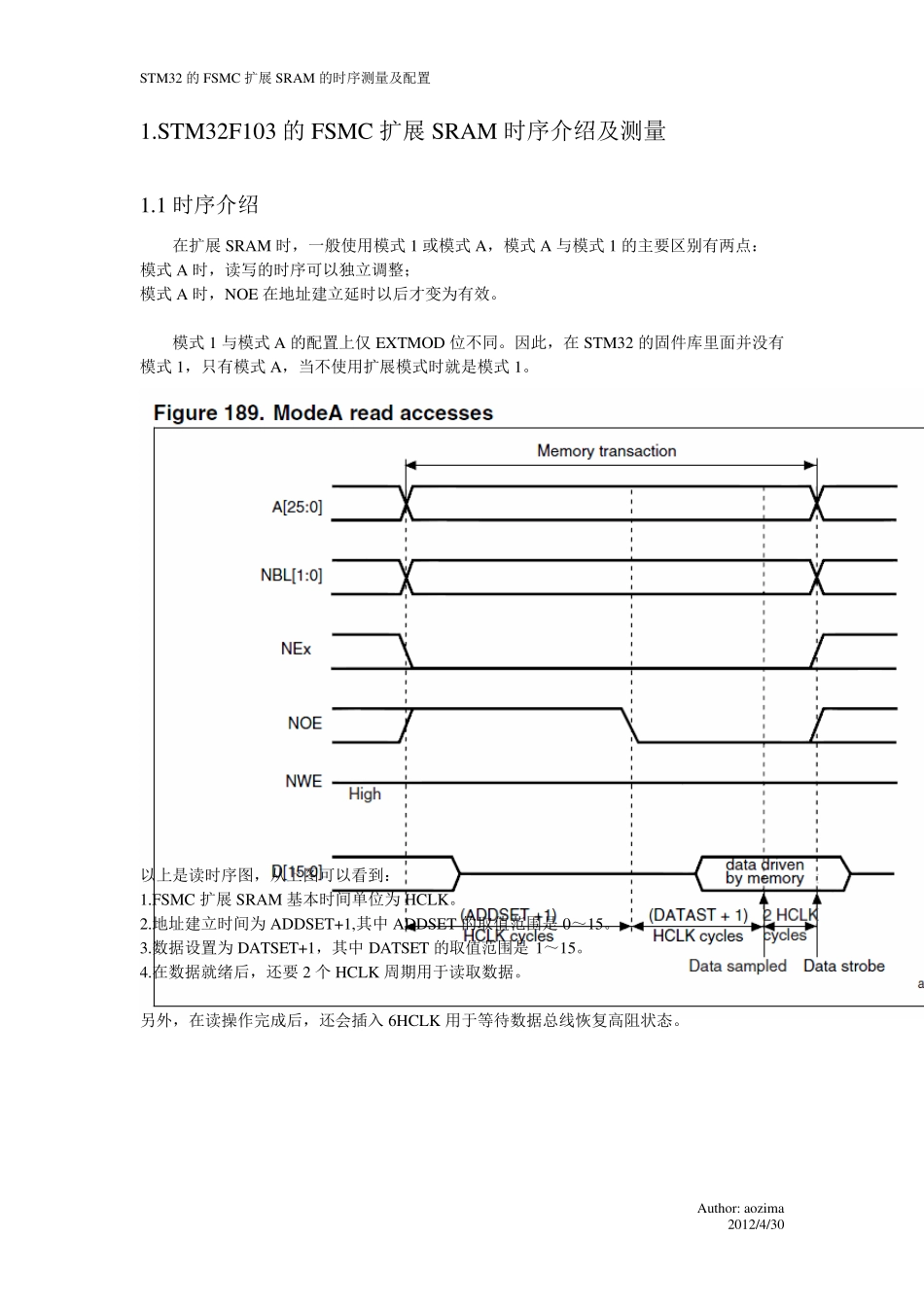

1 时序介绍 在扩展SRAM 时,一般使用模式1 或模式A,模式A 与模式1 的主要区别有两点: 模式A 时,读写的时序可以独立调整; 模式A 时,NOE 在地址建立延时以后才变为有效

模式1 与模式A 的配置上仅 EXTMOD 位不同

因此,在STM32 的固件库里面并没有模式1,只有模式A,当不使用扩展模式时就是模式1

以上是读时序图,从上图可以看到: 1

FSMC 扩展SRAM 基本时间单位为HCLK

地址建立时间为ADDSET+1,其中 ADDSET 的取值范围是 0~15

数据设置为DATSET+1,其中 DATSET 的取值范围是 1~15

在数据就绪后,还要2 个 HCLK 周期用于读取数据

另外,在读操作完成后,还会插入 6HCLK 用于等待数据总线恢复高阻状态

Author: aozima 2012/4/30 STM32 的FSMC 扩展SRAM 的时序测量及配置 以上是写时序图,从上图可以看到: 1

地址建立时间为ADDSET+1,其中ADDSET 的取值范围是0~15

数据设置为DATSET+1,其中DATSET 的取值范围是1~15

根据读写时序图我们可以计算出 STM32F103 的