实 验 二 十 进 制 计 数 器 实 验 该 实 验 将 使 用 Verilog 硬 件 描 述 语 言 在 DE2-70 开 发 平 台 上 设 计 一 个 基 本 时 序 逻 辑 电 路 ——1 位 十 进 制 计 数 器

通过这个 实 验 ,读者可以了解使 用 Quartus 工具设 计 硬 件 的基 本 流 程以及使 用 Quartus II 内置的工具进 行仿真的基 本 方法和使 用 SignalTap II 实 际观察电 路 运 行输出情况

SignalTap II 是 Quartus 工具的一 个 组件 ,是一 个 片上 的逻 辑 分析仪,可以通 过 JTAG 电 缆将 电 路 运行的实 际输出传回 Quartus 进 行观察,从而省去了外界逻 辑 分析仪 时 的很多麻烦

实 验 步骤 3

1 建立工程并完成硬 件 描 述 设 计 1

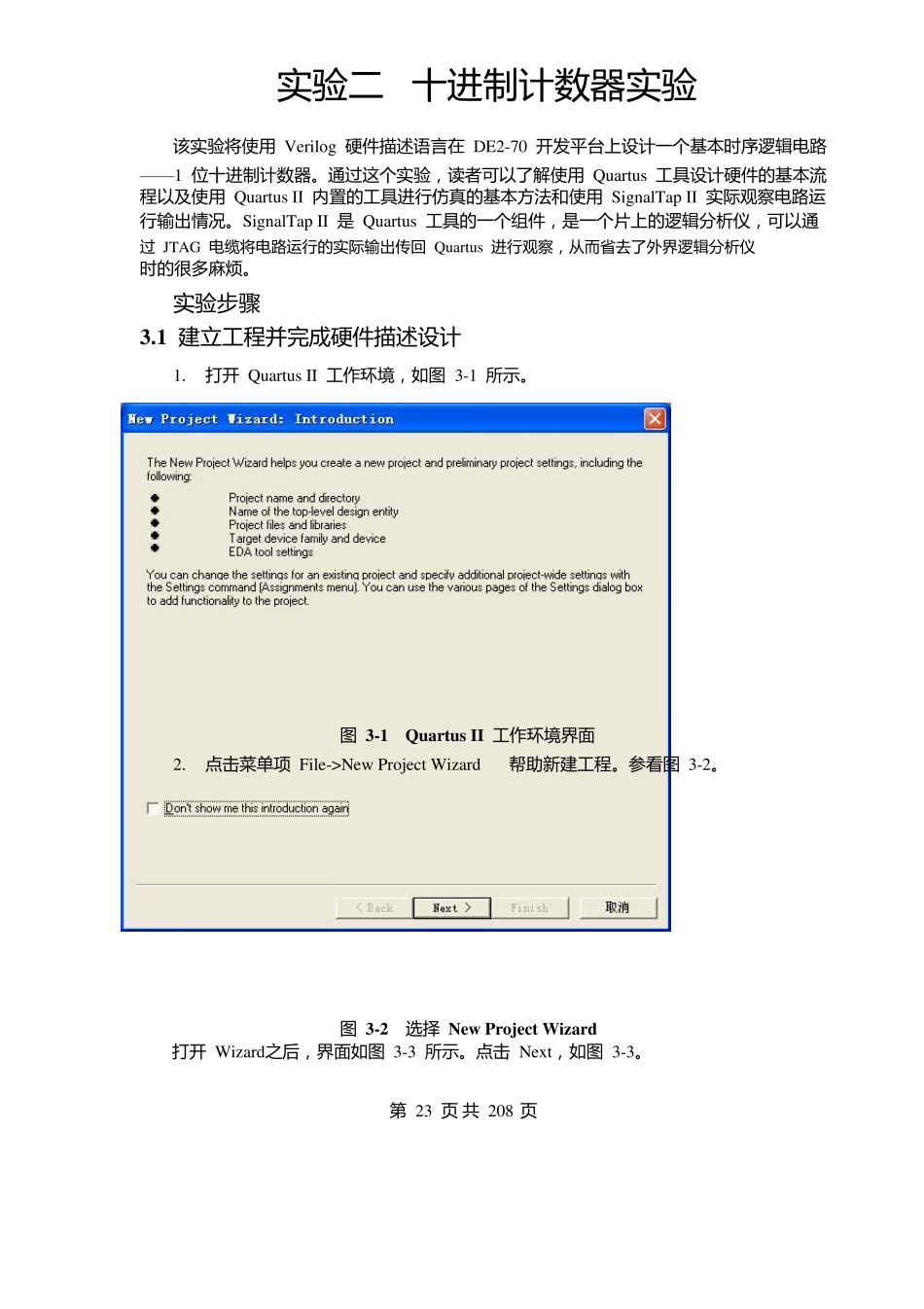

打开 Quartus II 工作环境,如图 3-1 所示

图 3-1 Quartus II 工作环境界面 2

点击菜单项 File->New Project Wizard 帮助新建工程

参看图 3-2

图 3-2 选择 New Project Wizard 打开 Wizard 之后,界面如图 3-3 所示

点击 Next,如图 3-3

第 23 页 共 208 页 实 验 二 十 进 制 计 数 器 实 验 图 3-3 New Project Wizard 界 面 3

输 入 工 程 工 作 路 径 、工 程 文件名以及顶层实 体名

这次实 验 会帮助读者理解顶层实 体名和工 程 名的关系,记住目前指定的工 程 名与顶层 实 体名都是 Cou nter10,输 入 结束后,如图 3-4 所示

点击 Nex t

图 3-4 输 入 设计 工 程 信息 4

添加设计 文件

界 面 如图 3-5 所示