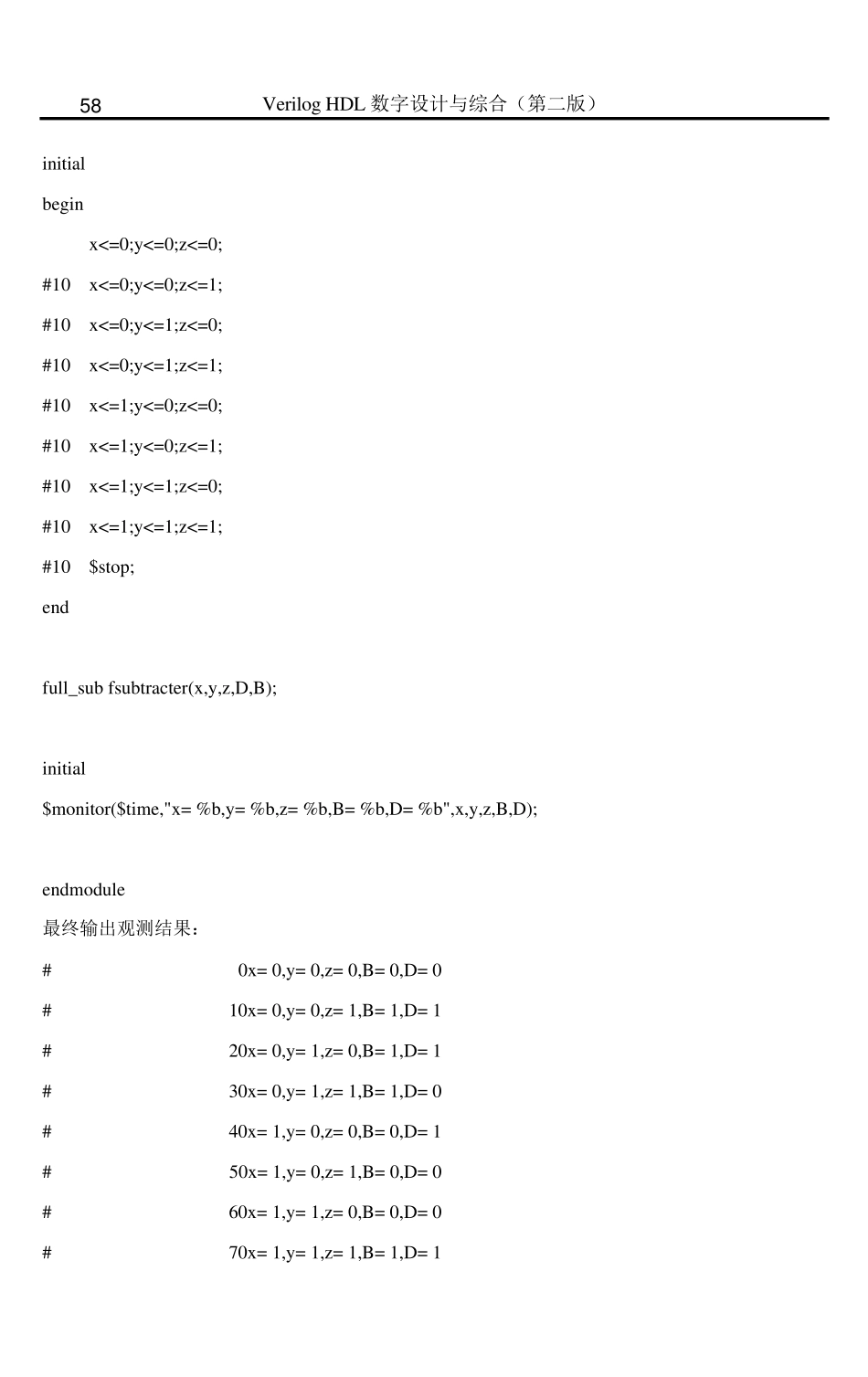

1.一个全减器具有三个一位输入:x,y 和z(前面的借位),两个一位输出D(差)和B(借位)。计算 D 和B 的逻辑等式如下所示: D = x’ y’ z’ + x’ y z’ + x y’ z’ + x y z B = x’ y + x’ z + y z 根据上面的定义写出Verilog 描述,包括 I/O 端口(注意:逻辑等式中的+对应于数据流建模中的逻辑或(| |)操作符)。编写激励块,在模块中实例引用全减器。对 x,y 和z 这三个输入的8 种组合及其对应的输出进行测试。 x y z B D 0 0 0 0 0 0 0 1 1 1 0 1 0 1 1 0 1 1 1 0 1 0 0 0 1 1 0 1 0 0 1 1 0 0 0 1 1 1 1 1 答:代码及测试激励如下:(D 应该= x’ y’ z + x’ y z’ + x y’ z’ + x y z) `timescale 1ns/1ns module full_sub(x,y,z,D,B); input x,y,z; output D,B; assign D=((!x)&(!y)&(z))||((!x)&y&(!z))||(x&(!y)&(!z))||(x&y&z); assign B=((!x)&y)||((!x)&z)||(y&z); endmodule module test61; reg x,y,z; wire D,B; Verilog HDL 数字设计与综合(第二版) 5 8 initial begin x<=0;y<=0;z<=0; #10 x<=0;y<=0;z<=1; #10 x<=0;y<=1;z<=0; #10 x<=0;y<=1;z<=1; #10 x<=1;y<=0;z<=0; #10 x<=1;y<=0;z<=1; #10 x<=1;y<=1;z<=0; #10 x<=1;y<=1;z<=1; #10 $stop; end full_sub fsubtracter(x,y,z,D,B); initial $monitor($time,"x= %b,y= %b,z= %b,B= %b,D= %b",x,y,z,B,D); endmodule 最终输出观测结果: # 0x= 0,y= 0,z= 0,B= 0,D= 0 # 10x= 0,y= 0,z= 1,B= 1,D= 1 # 20x= 0,y= 1,z= 0,B= 1,D= 1 # 30x= 0,y= 1,z= 1,B= 1,D= 0 # 40x= 1,y= 0,z= 0,B= 0,D= 1 # 50x= 1,y= 0,z= 1,B= 0,D= 0 # 60x= 1,y= 1,z= 0,B= 0,D= 0 # 70x= 1,y= 1,z= 1,B= 1,D= 1 第6 章 数据流建模 59 2.大小比较器的功能是比较两个数之间的关系:大于、小于或等于。一个四位大小比较器的输入是两个四位数A 和 B。我们可以将它们写成下面的形式,最左边的位为最高有效位: A =A(3) A(2) A(1) A(0) B =B(3) B(2) B(1) B(0) 两个数的比较可以从最高有效位开始,逐位进行。如果两个位不相等,则该位值为 0 的数为较小的数。...