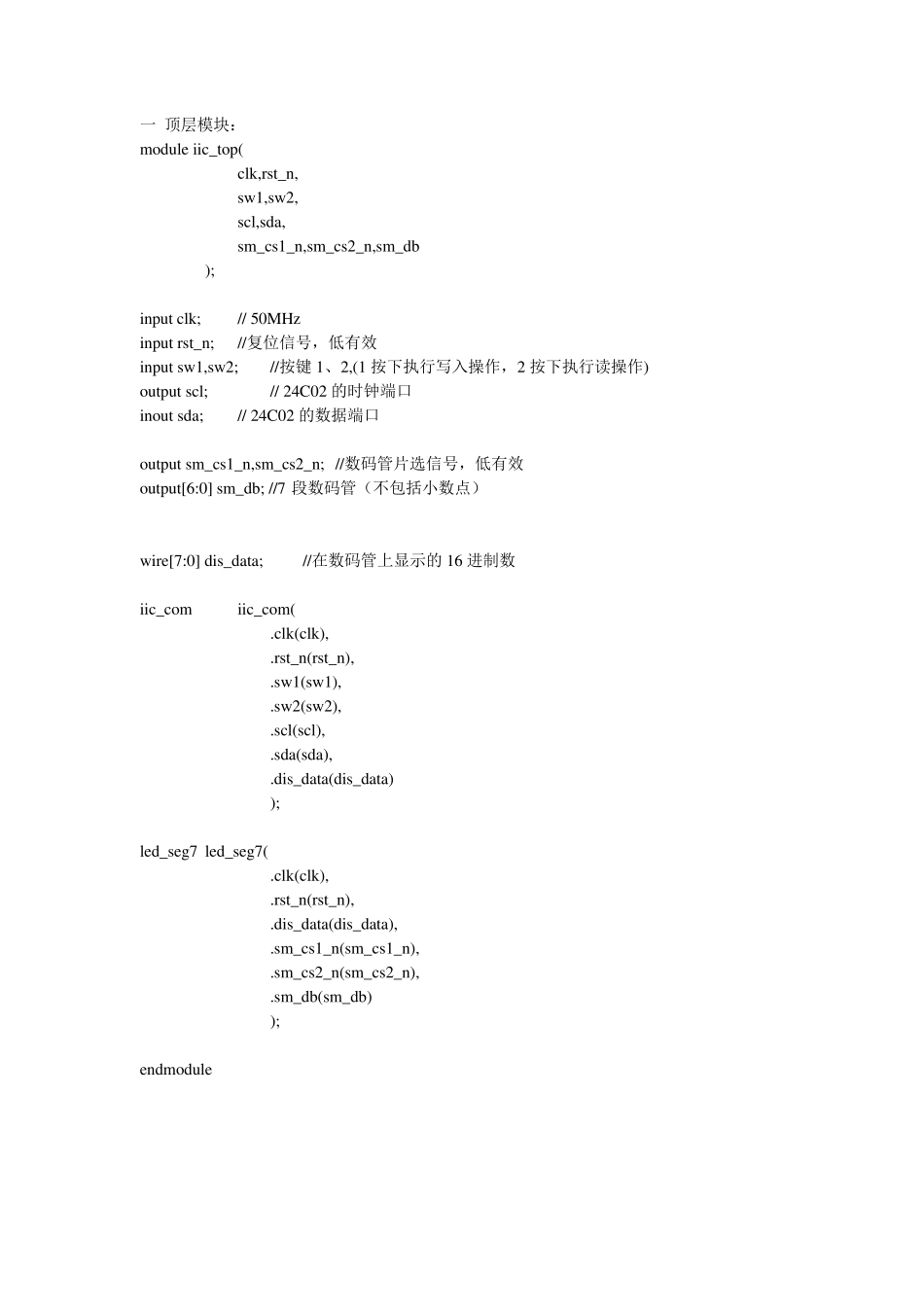

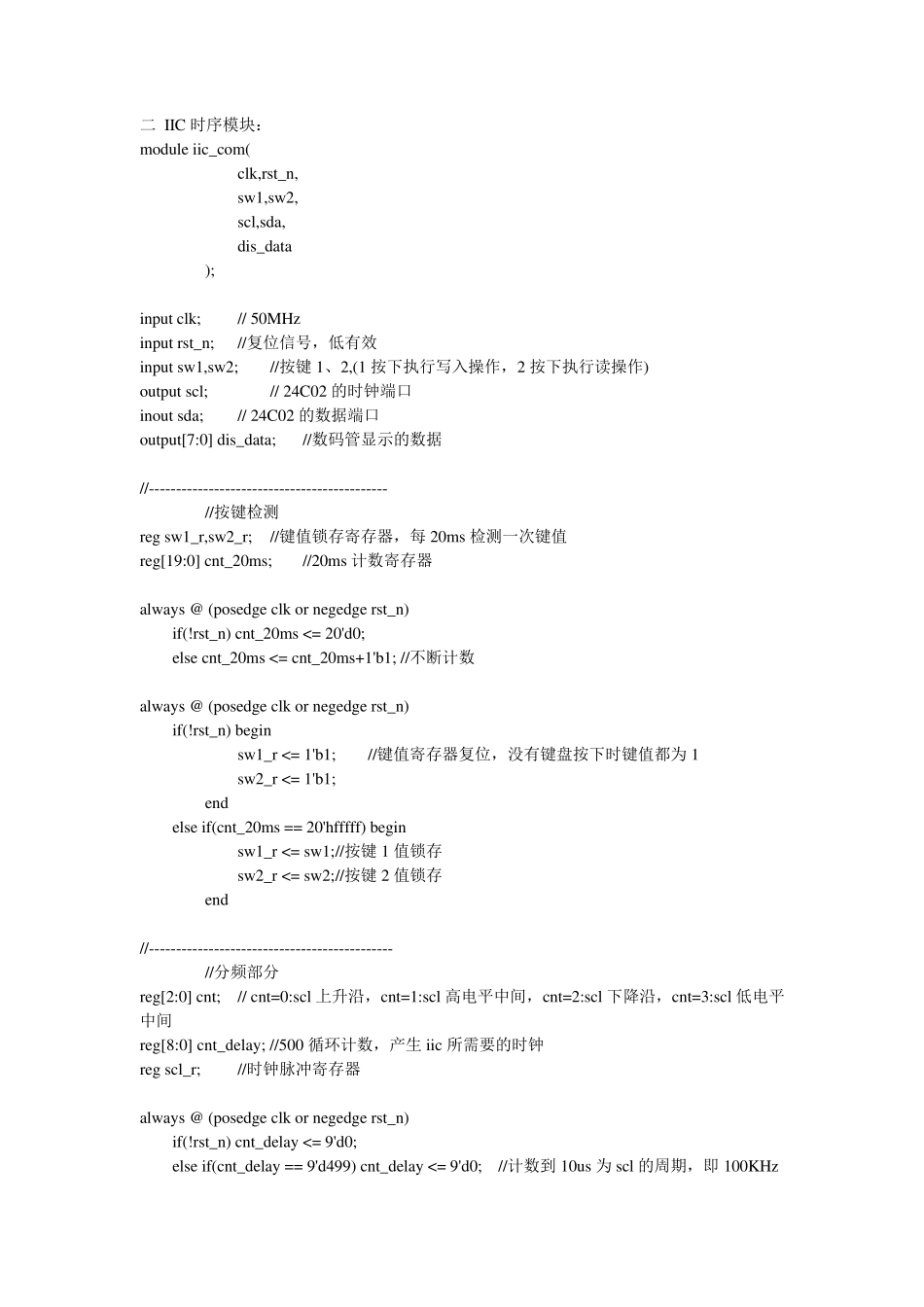

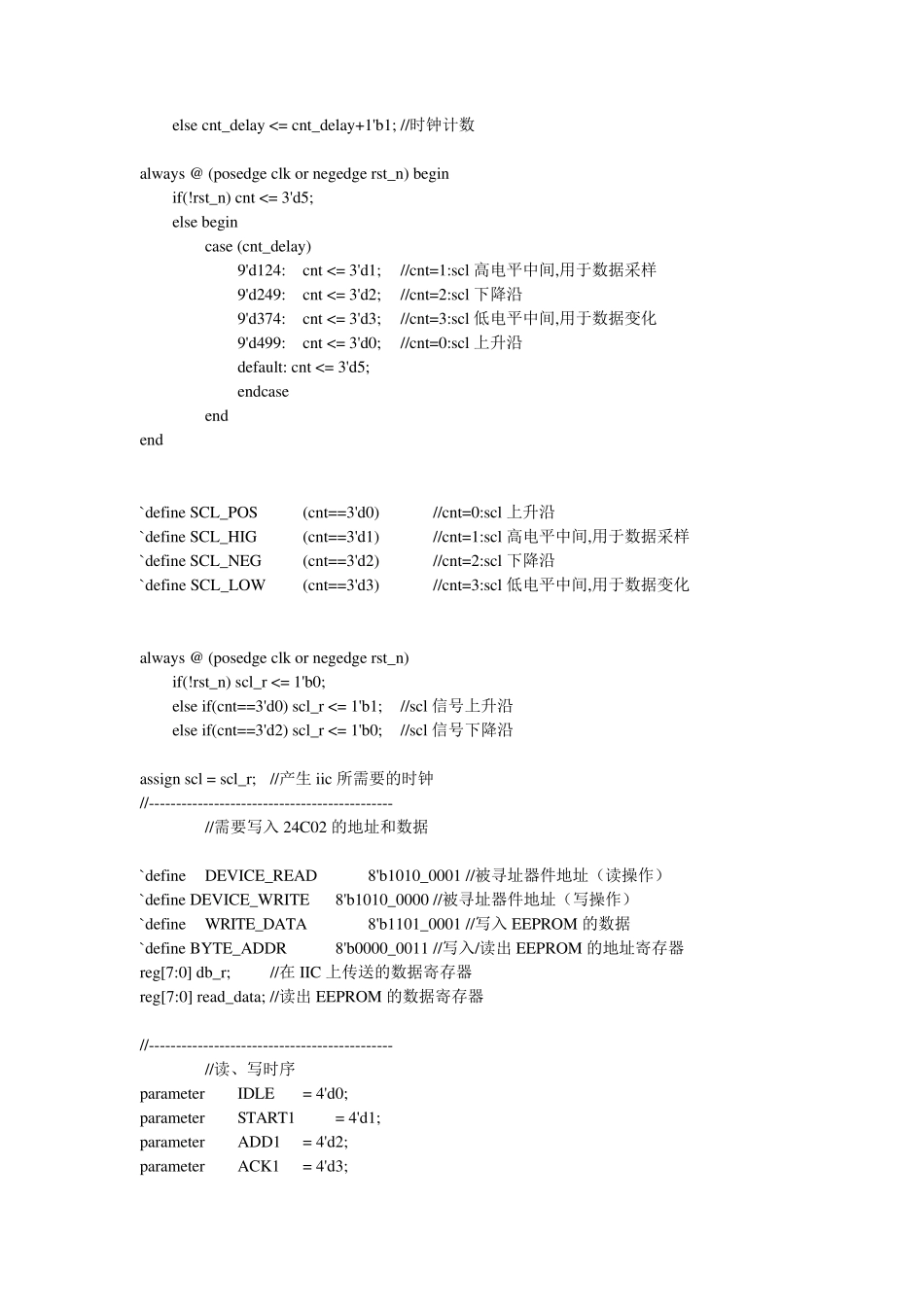

一 顶层模块: module iic_top( clk,rst_n, sw1,sw2, scl,sda, sm_cs1_n,sm_cs2_n,sm_db ); input clk; // 50MHz input rst_n; //复位信号,低有效 input sw1,sw2; //按键1、2,(1 按下执行写入操作,2 按下执行读操作) output scl; // 24C02 的时钟端口 inout sda; // 24C02 的数据端口 output sm_cs1_n,sm_cs2_n; //数码管片选信号,低有效 output[6:0] sm_db; //7 段数码管(不包括小数点) wire[7:0] dis_data; //在数码管上显示的 16 进制数 iic_com iic_com( .clk(clk), .rst_n(rst_n), .sw1(sw1), .sw2(sw2), .scl(scl), .sda(sda), .dis_data(dis_data) ); led_seg7 led_seg7( .clk(clk), .rst_n(rst_n), .dis_data(dis_data), .sm_cs1_n(sm_cs1_n), .sm_cs2_n(sm_cs2_n), .sm_db(sm_db) ); endmodule 二 IIC 时序模块: module iic_com( clk,rst_n, sw1,sw2, scl,sda, dis_data ); input clk; // 50MHz input rst_n; //复位信号,低有效 input sw1,sw2; //按键1、2,(1 按下执行写入操作,2 按下执行读操作) output scl; // 24C02 的时钟端口 inout sda; // 24C02 的数据端口 output[7:0] dis_data; //数码管显示的数据 //-------------------------------------------- //按键检测 reg sw1_r,sw2_r; //键值锁存寄存器,每 20ms 检测一次键值 reg[19:0] cnt_20ms; //20ms 计数寄存器 always @ (posedge clk or negedge rst_n) if(!rst_n) cnt_20ms <= 20'd0; else cnt_20ms <= cnt_20ms+1'b1; //不断计数 always @ (posedge clk or negedge rst_n) if(!rst_n) begin sw1_r <= 1'b1; //键值寄存器复位,没有键盘按下时键值都为 1 sw2_r <= 1'b1; end else if(cnt_20ms == 20'hfffff) begin sw1_r <= sw1; //按键1 值锁存 sw2_r <= sw2; //按键2 值锁存 end //--------------------------------------------- //分频部分 reg[2:0] cnt; // cnt=0:scl 上升沿,cnt=1:scl 高电平中间,cnt=2:scl 下降沿,cnt=3:scl 低电平中间 reg[8:0] cnt_delay; //500 循环计数,产生 iic 所需要的时钟 reg scl_r; //时钟脉冲寄存器 always @ (posedge clk or negedge rst_n) if(!rst_n) cnt_delay <= 9'd0; else if(cnt_delay == 9'd499) cnt_delay ...