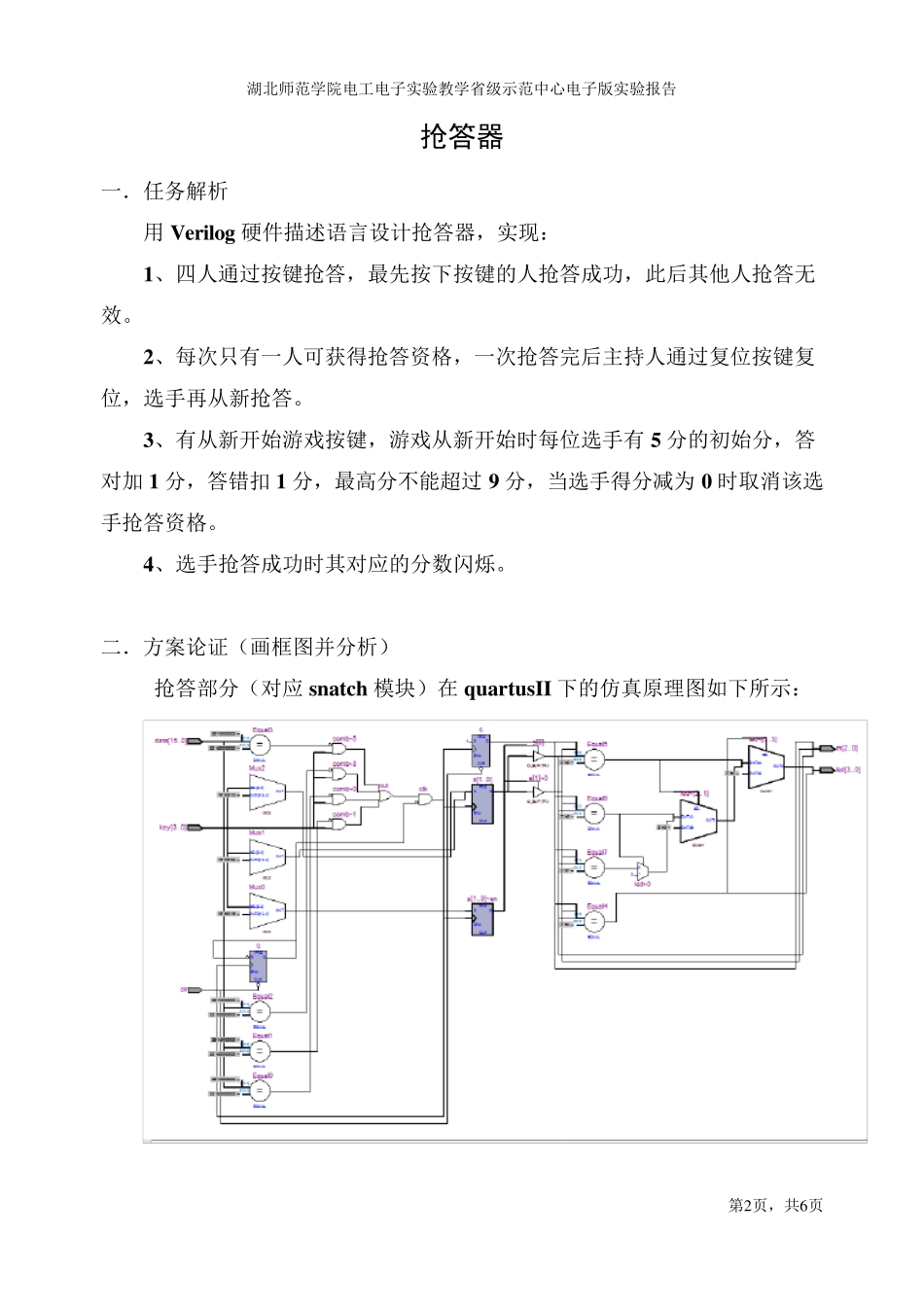

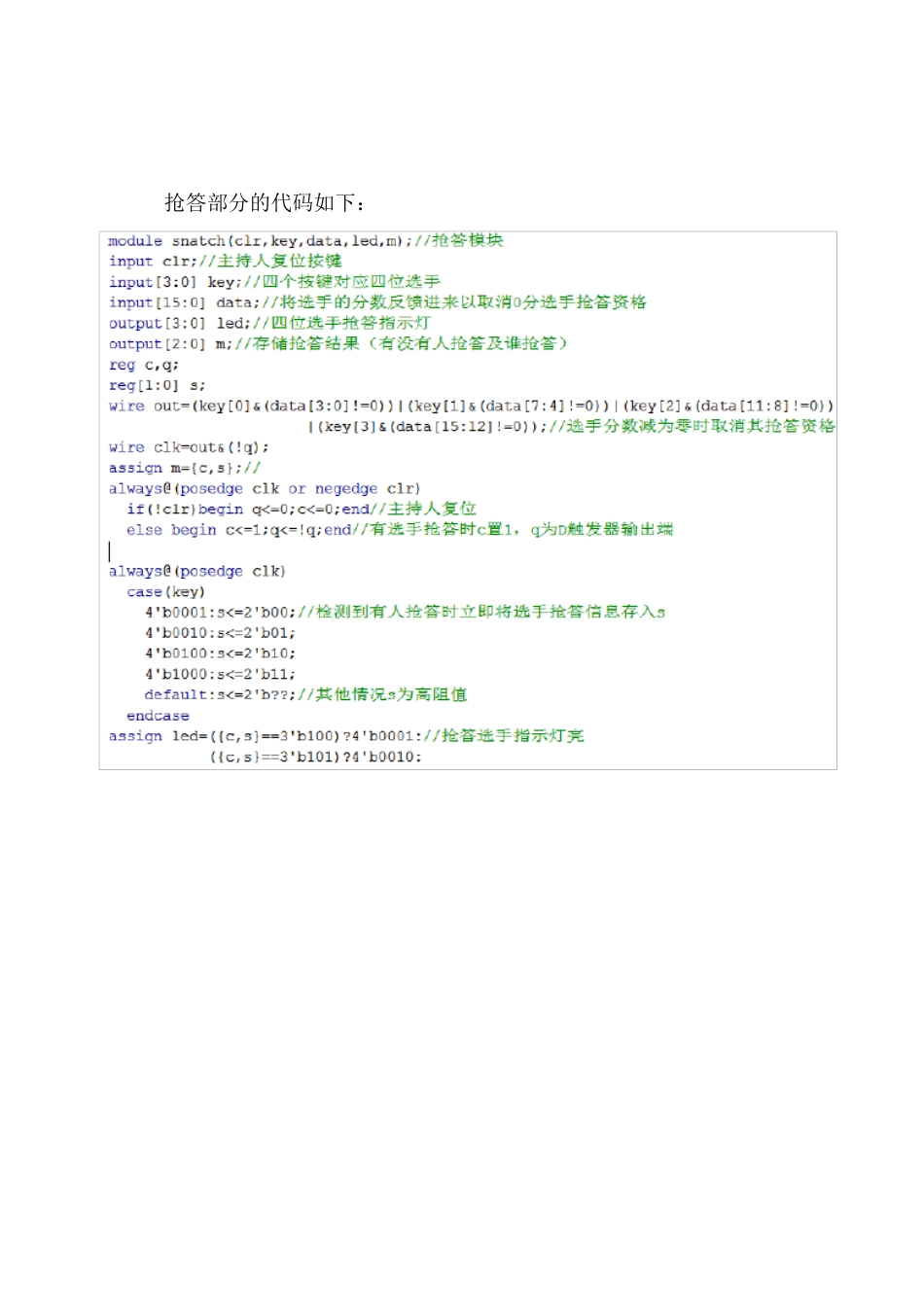

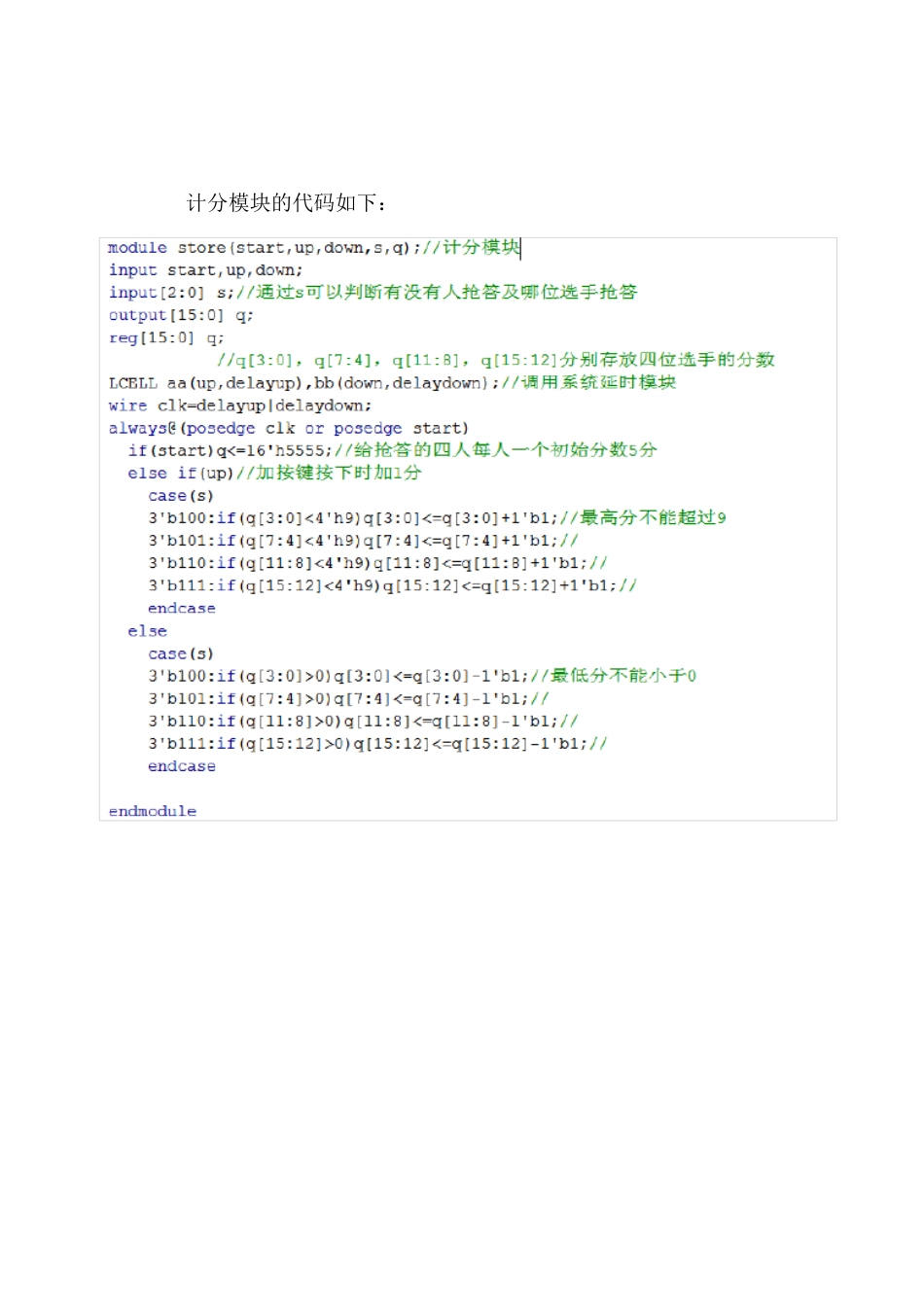

湖北师范学院电工电子实验教学省级示范中心电子版实验报告 第2 页,共6 页 抢答器 一.任务解析 用Verilog 硬件描述语言设计抢答器,实现: 1、四人通过按键抢答,最先按下按键的人抢答成功,此后其他人抢答无效。 2、每次只有一人可获得抢答资格,一次抢答完后主持人通过复位按键复位,选手再从新抢答。 3、有从新开始游戏按键,游戏从新开始时每位选手有 5 分的初始分,答对加 1 分,答错扣 1 分,最高分不能超过 9 分,当选手得分减为 0 时取消该选手抢答资格。 4、选手抢答成功时其对应的分数闪烁。 二.方案论证(画框图并分析) 抢答部分(对应 snatch 模块)在 qu artu sII 下的仿真原理图如下所示: 抢答部分的代码如下: 计分模块的代码如下: 顶层模块的代码如下: 三.重难点解析 抢答器的核心部分为巧妙地利用D 触发器的反馈,在检测到第一个上升沿时将按键(未按下时接低电平)接入的与门锁住,以保证与门只有一个上升沿输出,从而实现“最先按下按键的人抢答成功,此后其他人抢答无效”。在与门输出上升沿的同时检测按键,以确定是哪位选手抢答,用寄存器存下抢答选手的信息,最后确定哪个led 灯亮以及那位选手对应的分数闪烁。至于取消 0 分选手抢答资格,则是将各选手的分数反馈到选手抢答的按键,通过与门关闭相应选手按键上升沿的进入。其他功能的实现相对简单,在此不再赘述。 将各模块代码写好并测试后,在主模块中调用并分配引脚,引脚分配好后,从新编译、下载就可实验了。分别验证上述的各种功能,看是否达到预期的效果。 四.硬件资源分配(给出引脚分配说明) 芯片选用EP1K30TC114-3,clr 接全局清零键pin124,start(游戏从新开始键)接pin49,up(加分键)接pin47,down 接pin48,四个抢答按键key3、key2、key1、key0、分别接pin59、pin60、pin62、pin63,7 段数码管的 7 盏灯 a、b、c、d、e、f、g 分别 pin118、pin119、pin120、pin121、pin122、pin128、pin130,数码管选择信号 sel0、sel1、sel2 分别接pin132、pin133、pin135,抢答指示灯 led0、led1、led2、led3 分别接pin136、pin137、pin138、pin140。 五.结果分析 验证过程如下: 1、分别按下 start 和 clr 键,游戏处于初始状态,此时 8 个数码管等间隔地显示 4 个5 分,分数不闪烁。 2、按下 key0 键,此时 led0 亮,第一个分数闪烁,再按其他按键,数码管及灯的状态不变。按下 clr...