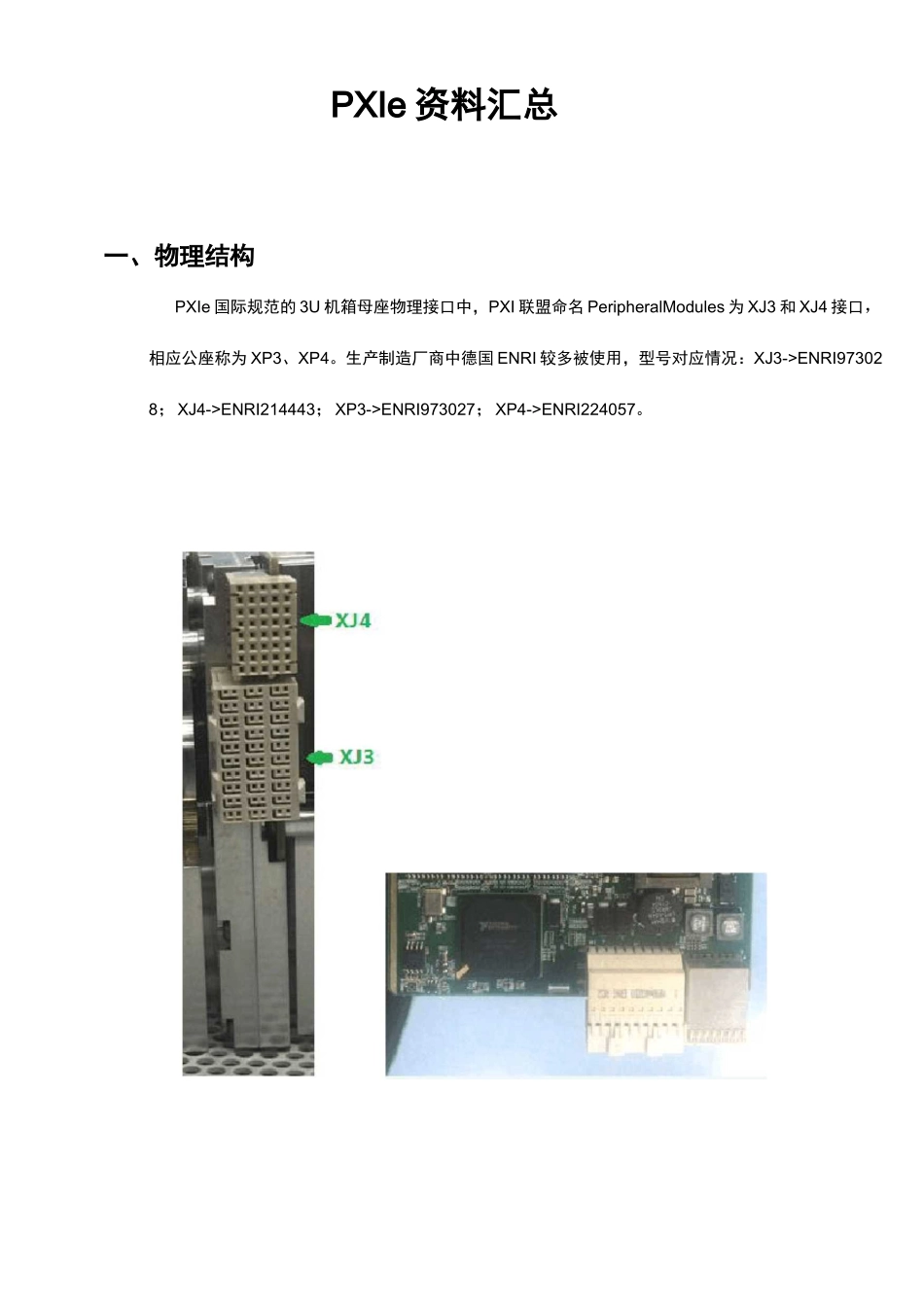

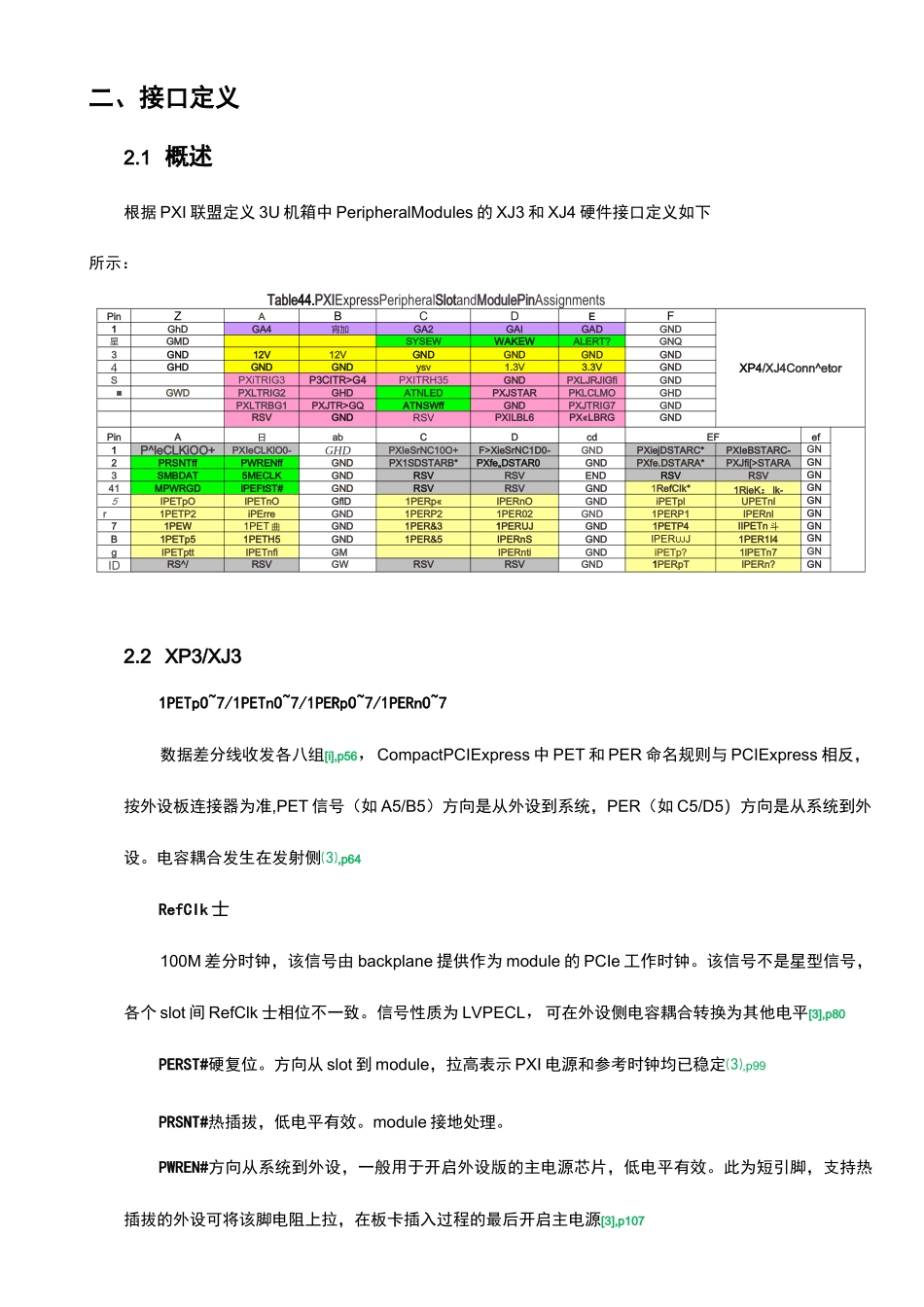

PXIe 母座底面PXIe 母座侧面PXIe 资料汇总一、物理结构PXIe 国际规范的 3U 机箱母座物理接口中,PXI 联盟命名 PeripheralModules 为 XJ3 和 XJ4 接口,相应公座称为 XP3、XP4

生产制造厂商中德国 ENRI 较多被使用,型号对应情况:XJ3->ENRI973028;XJ4->ENRI214443;XP3->ENRI973027;XP4->ENRI224057

二、接口定义2

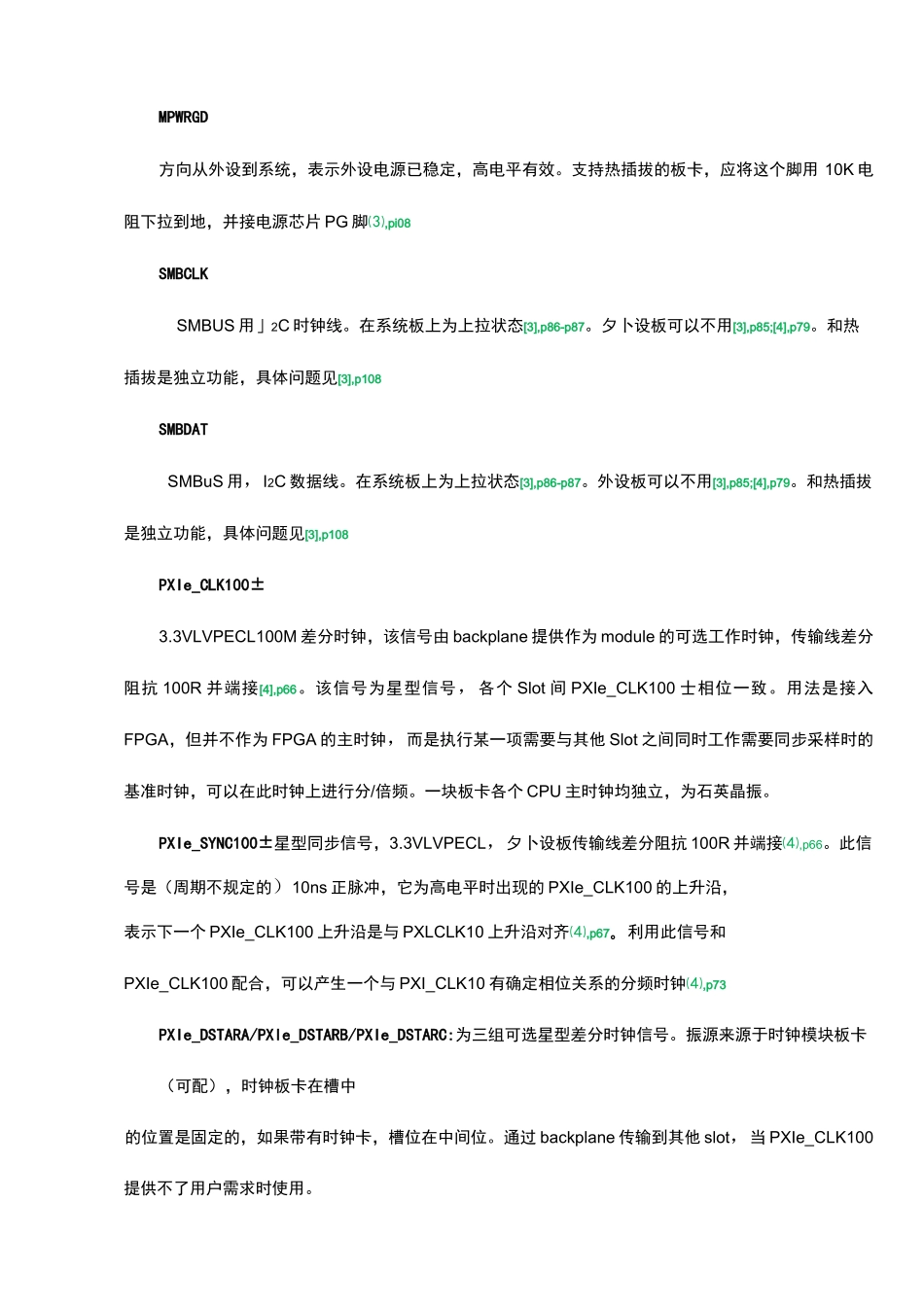

1 概述根据 PXI 联盟定义 3U 机箱中 PeripheralModules 的 XJ3 和 XJ4 硬件接口定义如下所示:Table44

PXIExpressPeripheralSlotandModulePinAssignmentsPinZABCDEFXP4/XJ4Conn^etor1GhDGA4宵加GA2GAIGADGND星GMDSYSEWWAKEWALERT

GNQ3GND12V12VGNDGNDGNDGND4GHDGNDGNDysv1

3VGNDSPXiTRIG3P3CITR>G4PXITRH35GNDPXLJRJlGfiGND■6GWDPXLTRIG2GHDATNLEDPXJSTARPKLCLMOGHDPXLTRBG1PXJTR>GQATNSWffGNDPXJTRIG7GNDRSVGNDRSVPXILBL6PX«LBRGGNDPinA日abCDcdEFef1P^leCLKiOO+PXIeCLKlO0-GHDPXIeSrNC10O+F>XieSrNC1D0-GNDPXiejDSTARC*PXIeBSTARC-GND2PRSNTffPWRENffGNDPX1SDSTARB*PXfe„DSTAR0GNDPXfe

DSTARA*PXJfi[>STARAGND3SMBDAT5MECLKGNDRSVRSVENDRSVRSVGND41MPWRGD