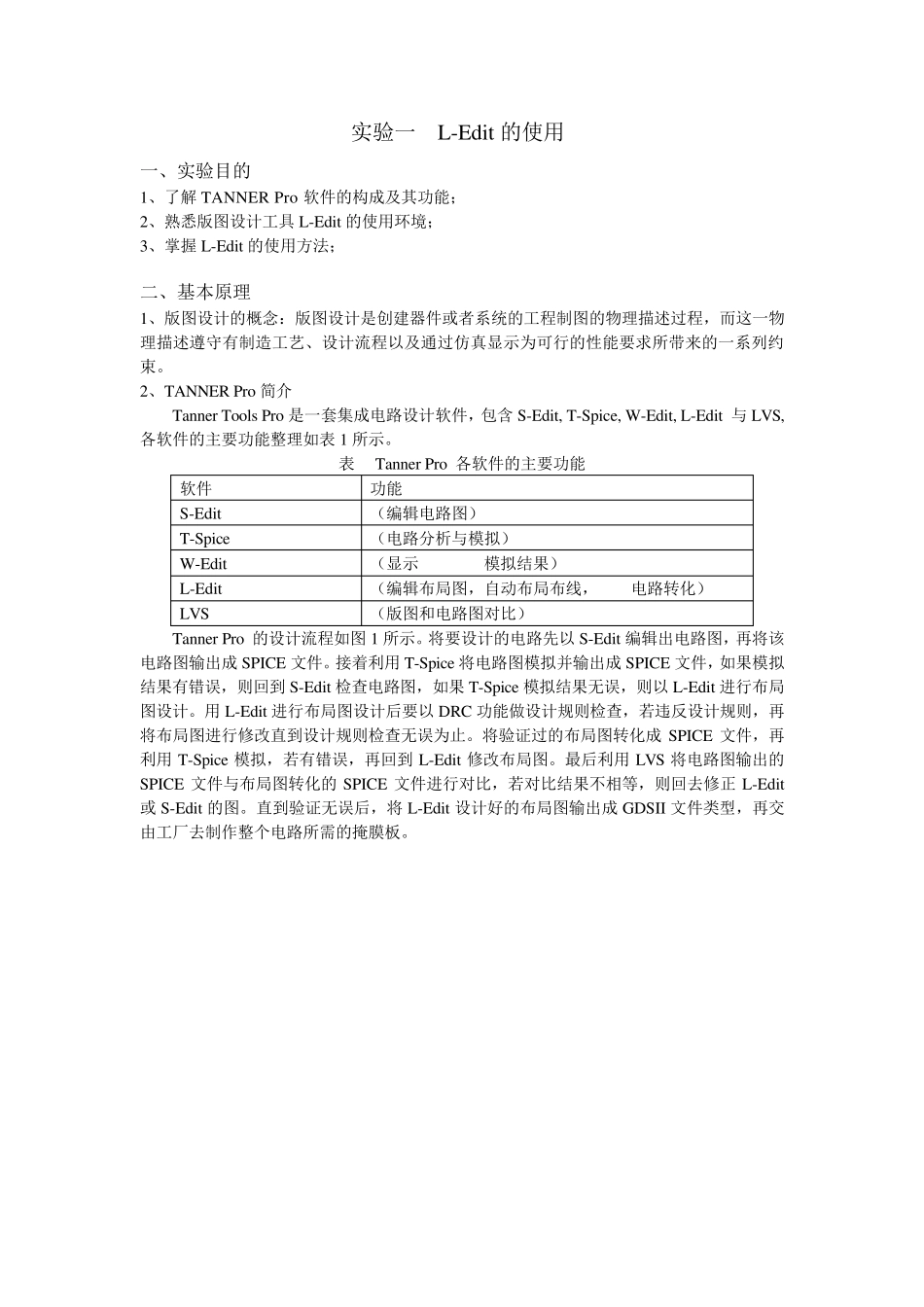

MEMS 原理实验(L-Edit)指导书 电子信息科学与技术 前 言 近年来,集成电路设计的发展非常迅速,许多设计必须借助于计算机辅助设计软件来完成,而大部分软件是在工作站上执行的,虽然其功能强大,但是价格昂贵,不利于初学者学习使用。目前,在个人电脑上开发的Tanner Pro 工具为用户提供了完整电路设计的环境,为初学者进入VLSI 设计领域提供了帮助。 Tanner 集成电路设计软件是由Tanner Research 公司开发的基于Window s平台的用于集成电路设计的工具软件。该软件功能十分强大,易学易用,包括S-Edit,T-Spice,W-Edit,L-Edit 与LVS,从电路设计、分析模拟到电路布局一应俱全。其中的L-Edit 版图编辑器在国内应用广泛,具有很高知名度,它不仅可以用于传统的集成电路设计,还可以用于MEMS 版图设计,具有强大的集成电路设计、模拟验证、版图编辑和自动布局布线等功能,图形处理速度快、编辑功能强、通俗易学、使用方便,很适用于个人进行集成电路设计或其它微细图形加工的版图设计工作。将其作为《MEMS 原理》课程的实验课程,旨在通过对 L-edit 学习,掌握版图设计的基本流程。 实验一 L-Edit的使用 一、实验目的 1、了解 TANNER Pro 软件的构成及其功能; 2、熟悉版图设计工具 L-Edit的使用环境; 3、掌握 L-Edit的使用方法; 二、基本原理 1、版图设计的概念:版图设计是创建器件或者系统的工程制图的物理描述过程,而这一物理描述遵守有制造工艺、设计流程以及通过仿真显示为可行的性能要求所带来的一系列约束。 2、TANNER Pro 简介 Tanner Tools Pro 是一套集成电路设计软件,包含 S-Edit, T-Spice, W-Edit, L-Edit 与 LVS,各软件的主要功能整理如表 1 所示。 表 1 Tanner Pro 各软件的主要功能 软件 功能 S-Edit (编辑电路图) T-Spice (电路分析与模拟) W-Edit (显示 T-Spice模拟结果) L-Edit (编辑布局图,自动布局布线,DRC,电路转化) LVS (版图和电路图对比) Tanner Pro 的设计流程如图 1 所示。将要设计的电路先以 S-Edit编辑出电路图,再将该电路图输出成 SPICE 文件。接着利用T-Spice 将电路图模拟并输出成 SPICE 文件,如果模拟结果有错误,则回到 S-Edit检查电路图,如果 T-Spice 模拟结果无误,则以 L-Edit进行布局图设计。用L-Edit进行布局图设计后要以 DRC 功能做设计规则检查,若违反设计规则,再将布局图进行修改直到设计规则...