Wishbone 简介 一、背景介绍 随着以 IP 核复用为基础的 SoC 设计技术的发展,工业界及研究组织积极从事相关 IP互联标准方案的制定工作,从目前的研究和发展看,影响力较大的有 IBM 公司的CoreConnect、ARM 公司的 AMBA 和 Silicore Corp 公司的 Wishbone

Wishbone 现在由 OpenCores 组织维护,是 OpenCores 建议的片上总线标准,目前已有大量开源的 IP Core 使用 Wishbone 总线作为互连标准

Wishbone 总线只定义了信号和信号间的时序关系,因此可用于软核、固核和硬核,对硬件描述语言、综合工具和实现手段没有特殊要求

与其他片上总线相比,Wishbone 总线结构简单,互连灵活,对用户定制的支持良好,与其他片上总线的互连也较简单,因此随着 SOPC 技术的发展,有着广泛应用前景

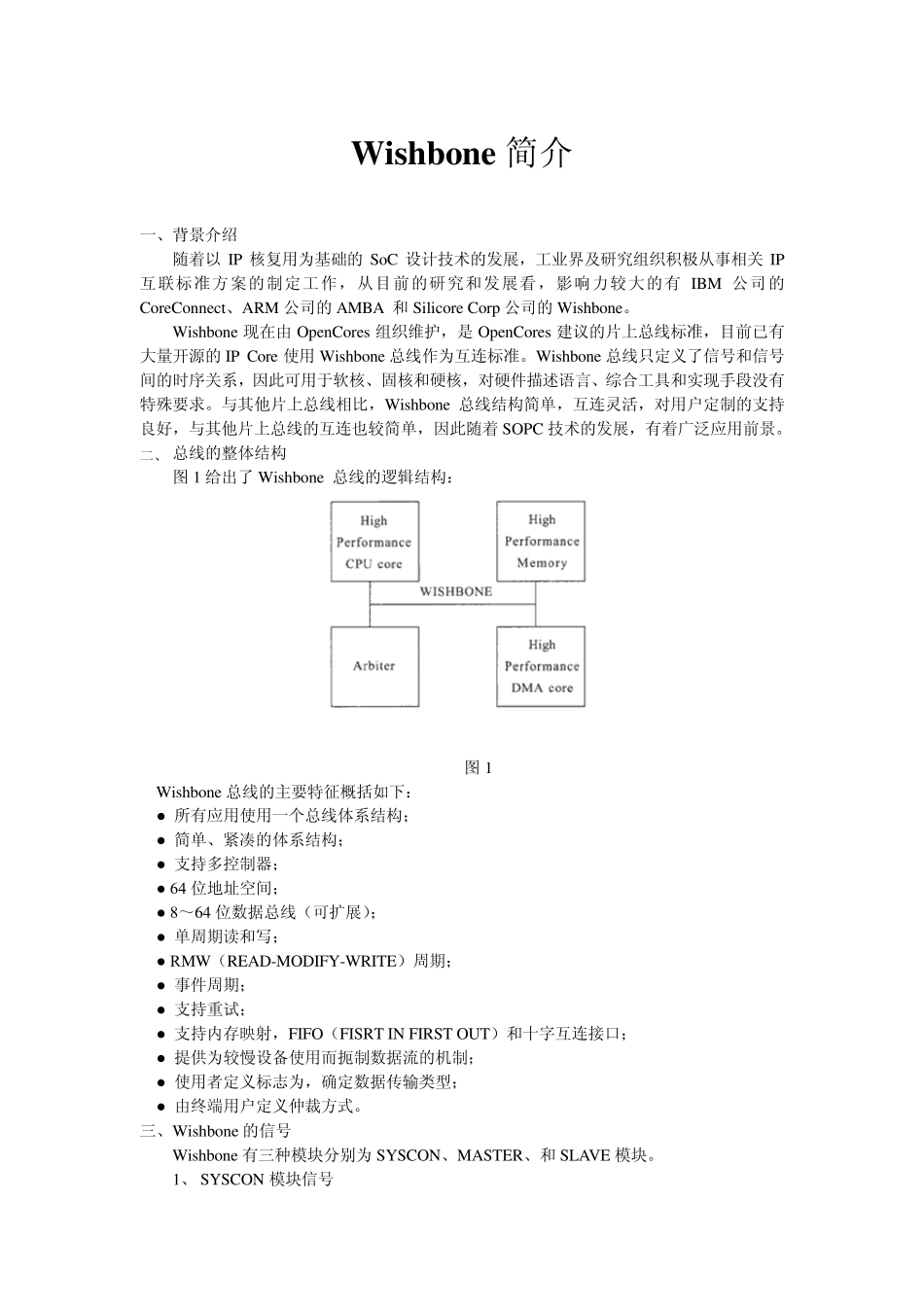

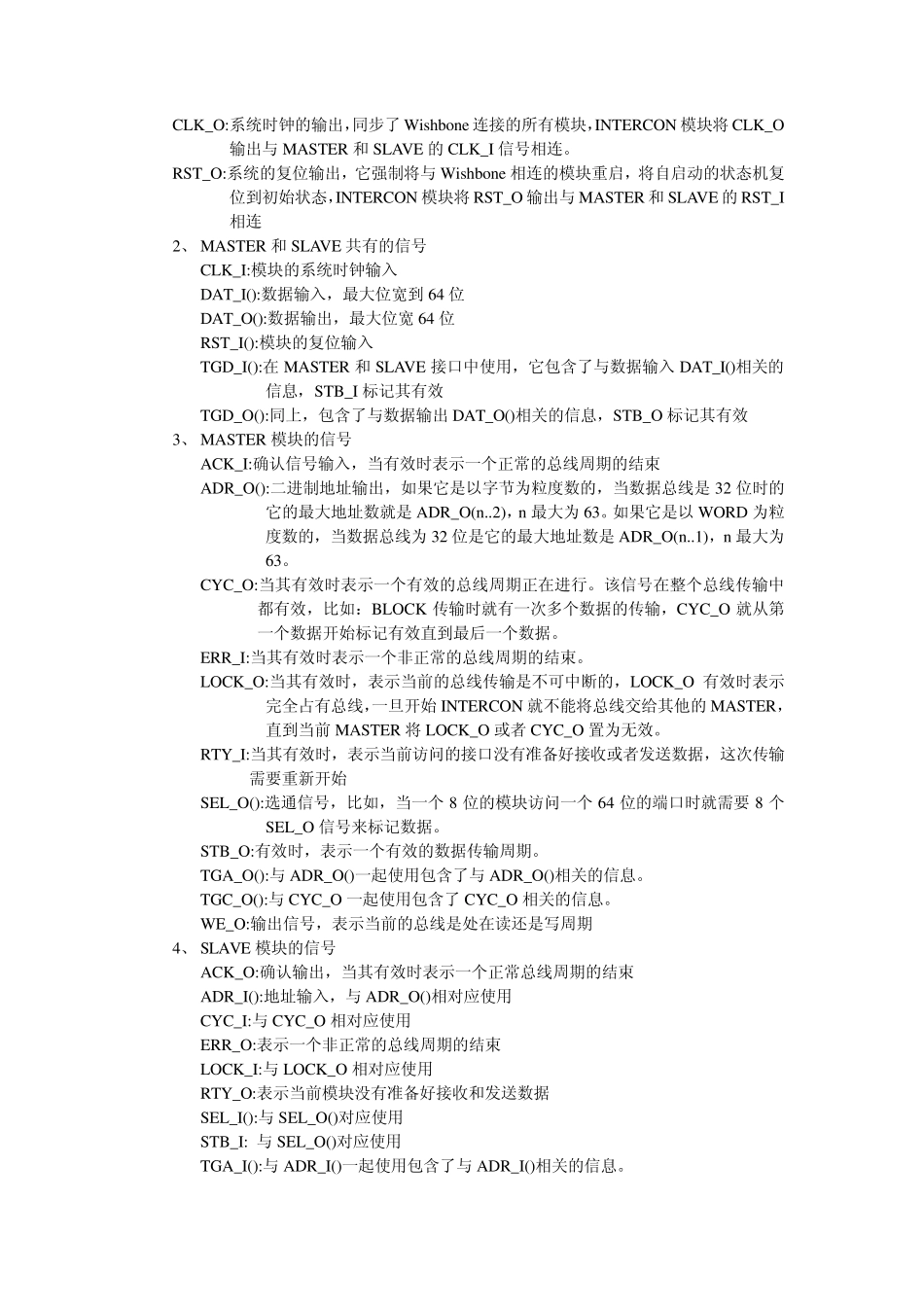

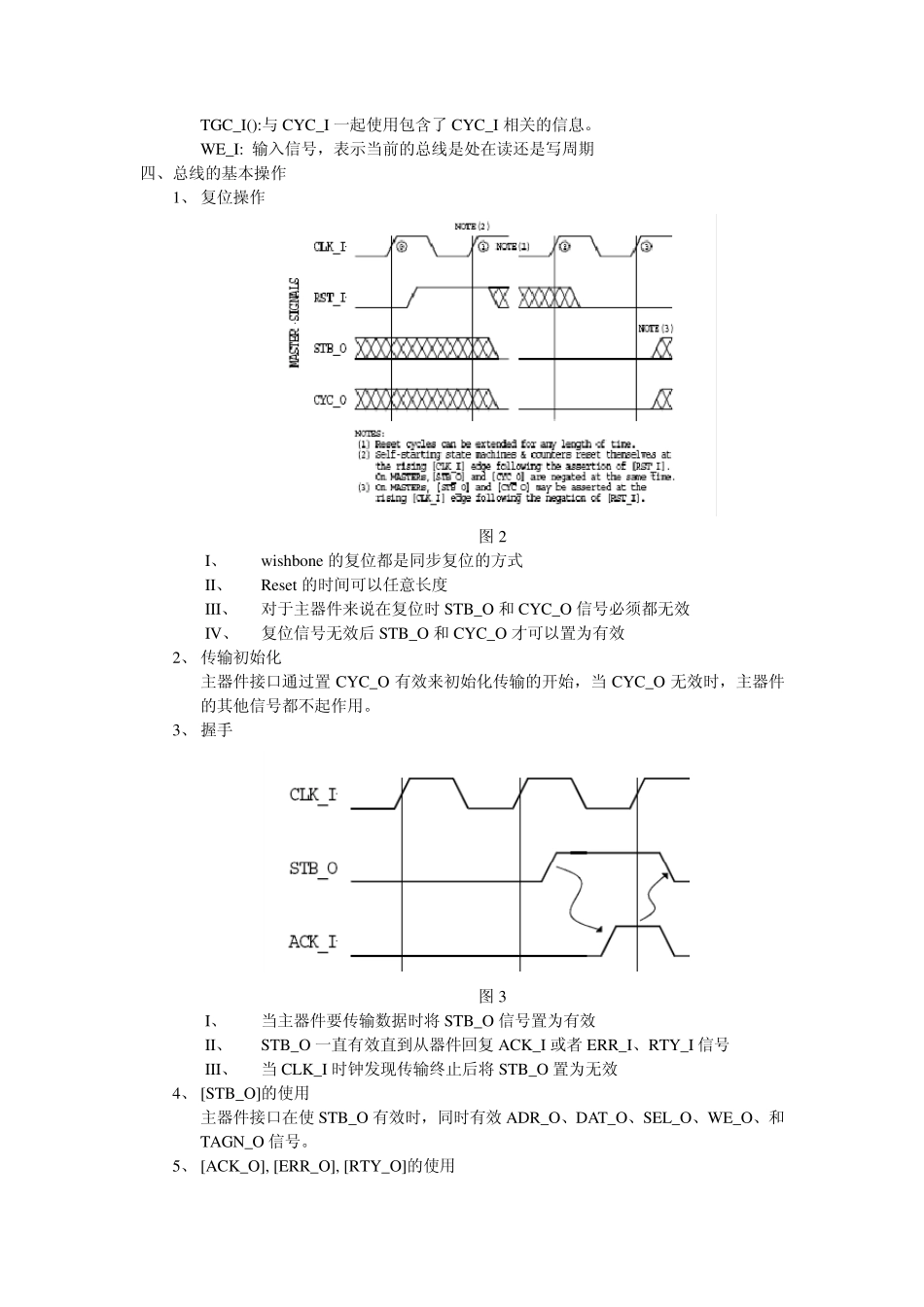

二、 总线的整体结构 图 1 给出了 Wishbone 总线的逻辑结构: 图 1 Wishbone 总线的主要特征概括如下: ● 所有应用使用一个总线体系结构; ● 简单、紧凑的体系结构; ● 支持多控制器; ● 64 位地址空间; ● 8~64 位数据总线(可扩展); ● 单周期读和写; ● RMW(READ-MODIFY-WRITE)周期; ● 事件周期; ● 支持重试; ● 支持内存映射,FIFO(FISRT IN FIRST OUT)和十字互连接口; ● 提供为较慢设备使用而扼制数据流的机制; ● 使用者定义标志为,确定数据传输类型; ● 由终端用户定义仲裁方式

三、Wishbone 的信号 Wishbone 有三种模块分别为 SYSCON、MASTER、和 SLAVE 模块

1、 SYSCON 模块信号 CLK_O:系统时钟的输出,同步了Wishbone 连接的所有模块,INTERCON