功能仿真和时序仿真 章节:第 3 章 第 2节 3

2 功能仿真与时序仿真 3

1 概述 仿真过程是正确实现设计的关键环节,用来验证设计者的设计思想是否正确,及在设计实现过程中各种分布参数引入后,其设计的功能是否依然正确无误

仿真主要分为功能仿真和时序仿真

功能仿真是在设计输入后进行; 时序仿真是在逻辑综合后或布局布线后进行

功能仿真 ( 前仿真 ) 功能仿真是指在一个设计中, 在设计实现前对所创建的逻辑进行的验证其功能是否正确的过程

布局布线以前的仿真都称作功能仿真, 它包括综合前仿真( Pre-Synthesis Simulation )和综合后仿真( Post-Synthesis Simulation )

综合前仿真主要针对基于原理框图的设计 ; 综合后仿真既适合原理图设计 , 也适合基于 HDL 语言的设计

时序仿真(后仿真) 时序仿真使用布局布线后器件给出的模块和连线的延时信息, 在最坏的情况下对电路的行为作出实际地估价

时序仿真使用的仿真器和功能仿真使用的仿真器是相同的, 所需的流程和激励也是相同的; 惟一的差别是为时序仿真加载到仿真器的设计包括基于实际布局布线设计的最坏情况的布局布线延时, 并且在仿真结果波形图中,时序仿真后的信号加载了时延, 而功能仿真没有

2 仿真工具 1

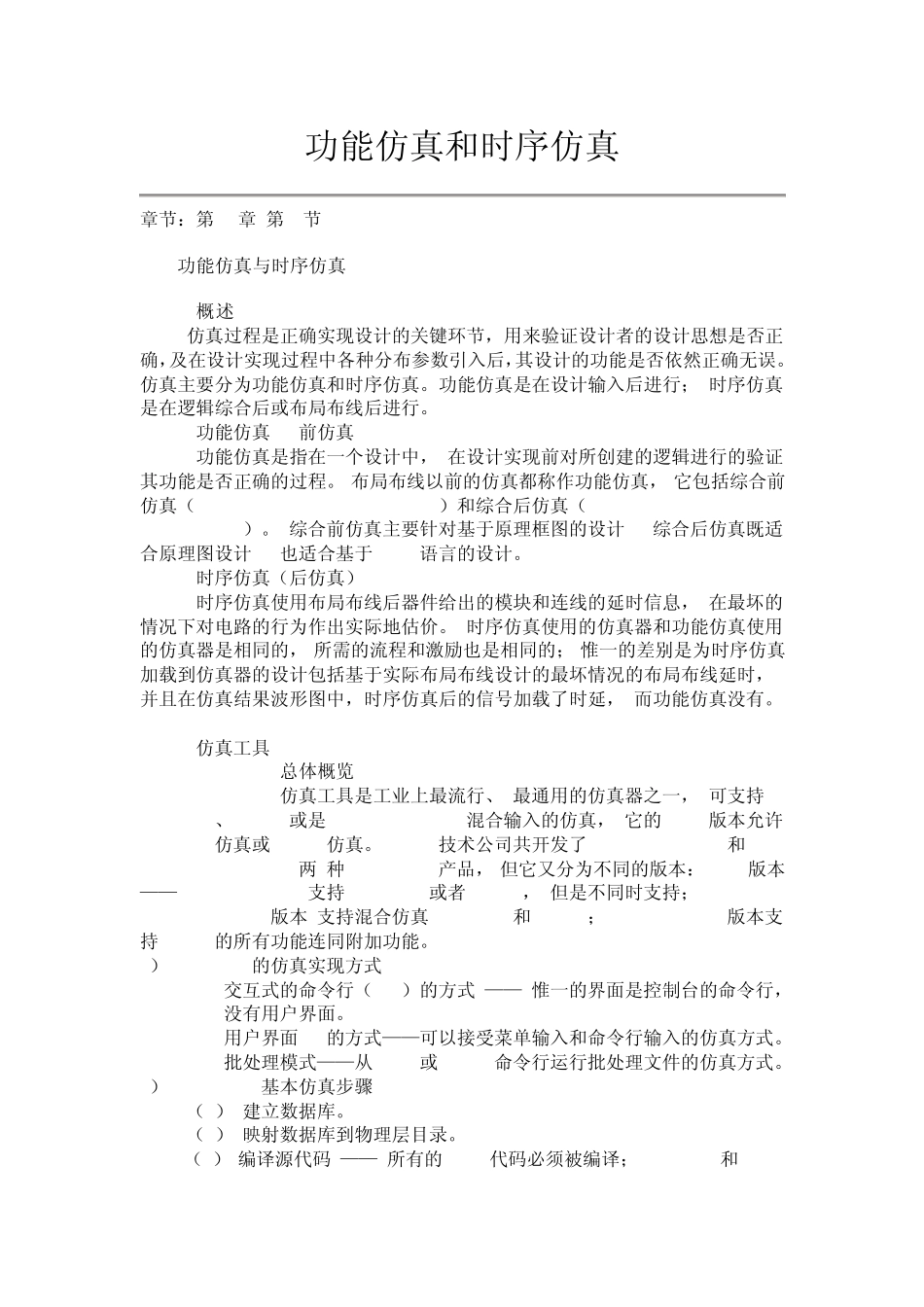

ModelSim 总体概览 ModelSim 仿真工具是工业上最流行、 最通用的仿真器之一, 可支持 Verilog 、 VHDL 或是 VHDL/ Verilog 混合输入的仿真, 它的 OEM 版本允许 Verilog 仿真或 VHDL 仿真

Model 技术公司共开发了 ModelSim/VHDL 和 ModelSim/Verilog 两 种 ModelSim 产品, 但它又分为不同的版本: OEM 版本 —— ModelSim/LNL 支持