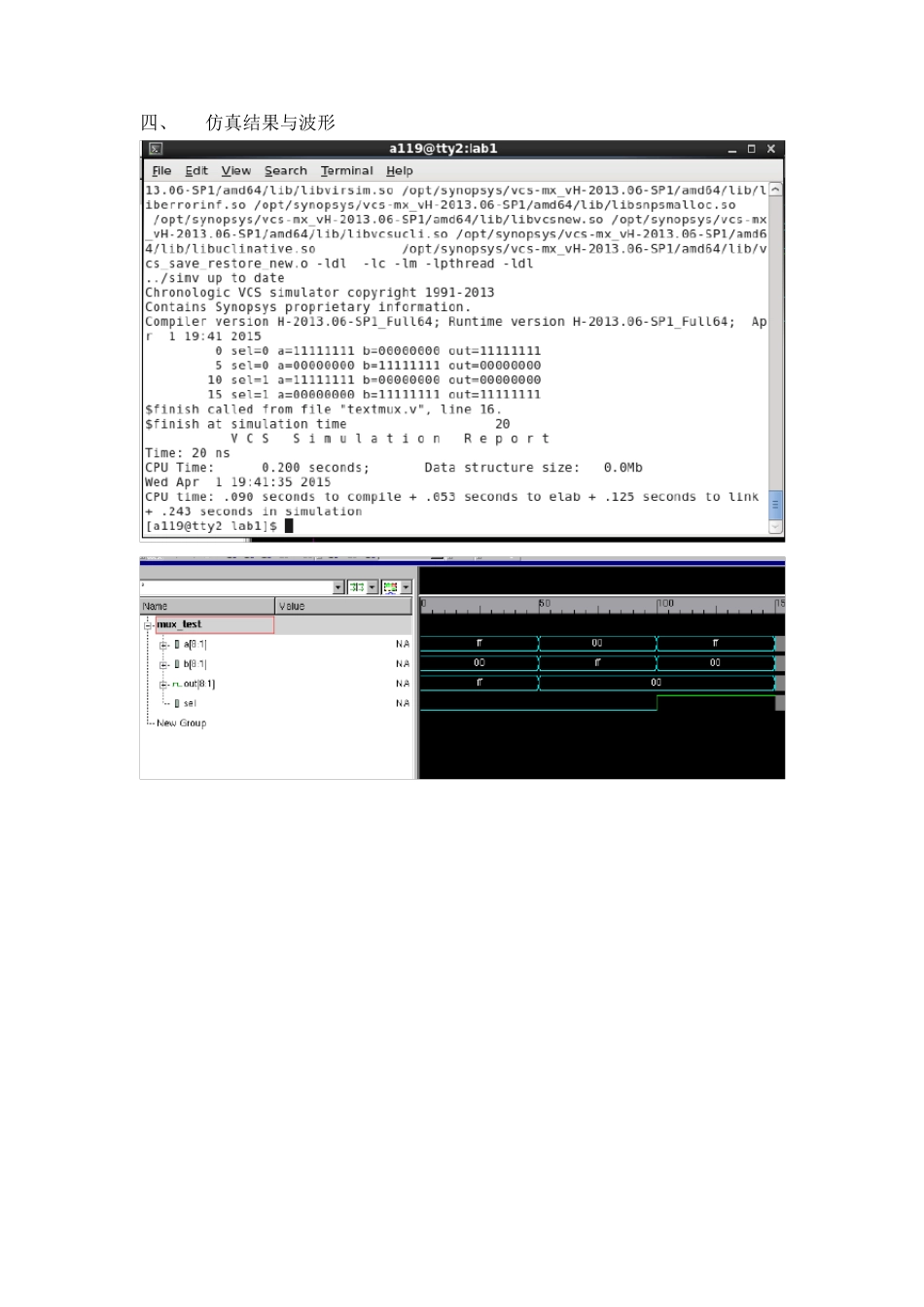

电子工程学院 AS IC 专业实验报告 班级: 姓名: 学号: 班内序号: 第一部分 语言级仿真 LAB 1:简单的组合逻辑设计 一、 实验目的 掌握基本组合逻辑电路的实现方法。 二、 实验原理 本实验中描述的是一个可综合的二选一开关,它的功能是当 sel = 0 时,给出 out = a,否则给出结果 out = b。在 Verilog HDL 中,描述组合逻辑时常使用 assign 结构。equal=(a==b)?1:0 是一种在组合逻辑实现分支判断时常用的格式。parameter 定义的size参数决定位宽。测试模块用于检测模块设计的是否正确,它给出模块的输入信号,观察模块的内部信号和输出信号。 三、 源代码 mux.v module scale_mux(out,sel,b,a); parameter size=1; output[size-1:0] out; input[size-1:0]b,a; input sel; assign out = (!sel)?a: (sel)?b: {size{1'bx}}; endmodule mux_test.v `define width 8 `timescale 1 ns/1 ns module mux_test; reg[`width:1]a,b; wire[`width:1]out; reg sel; scale_mux#(`width)m1(.out(out),.sel(sel),.b(b),.a(a)); initial begin $monitor($stime,,"sel=%b a=%b b=%b out=%b",sel,a,b,out); $dumpvars(2,mux_test); sel=0;b={`width{1'b0}};a={`width{1'b1}}; #5sel=0;b={`width{1'b1}};a={`width{1'b0}}; #5sel=1;b={`width{1'b0}};a={`width{1'b1}}; #5sel=1;b={`width{1'b1}};a={`width{1'b0}}; #5 $finish; end endmodule 四、 仿真结果与波形 LAB 2:简单时序逻辑电路的设计 一、 实验目的 掌握基本时序逻辑电路的实现。 二、 实验原理 在 Verilog HDL 中,相对于组合逻辑电路,时序逻辑电路也有规定的表述方式。在可综合的Verilog HDL 模型中,我们常使用 always 块和@(posedge clk)或@(negedge clk)的结构来表述时序逻辑。 在 always 块中,被赋值的信号都必须定义为 reg 型,这是由时序逻辑电路的特点所决定的对于 reg 型数据,如果未对它进行赋值,仿真工具会认为它是不定态。为了正确地观察到仿真结果,在可综合的模块中我们通常定义一个复位信号 rst-,当它为低电平时对电路中的寄存器进行复位。 三、 源代码 counter.v `timescale 1 ns/100 ps module counter(cnt,clk,data,rst_,load); output[4:0]cnt ; input [4:0]data; input clk; input rst_; input load; reg [4:0]cnt; always@(posedge ...