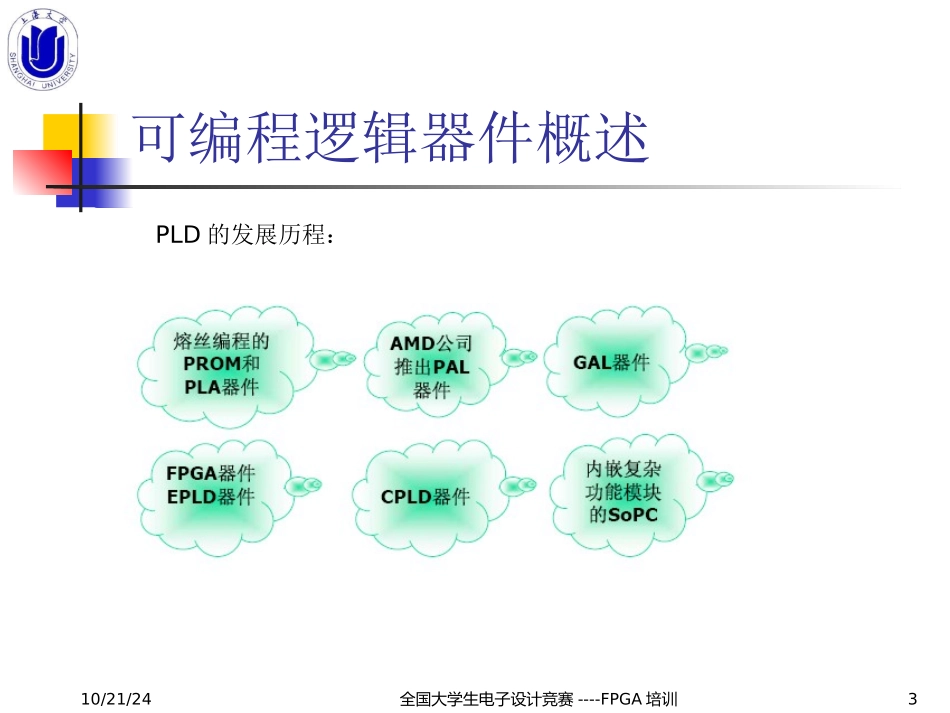

10/21/24----FPGA全国大学生电子设计竞赛培训1FPGA培训课件10/21/24全国大学生电子设计竞赛----FPGA培训2第一讲内容可编程逻辑器件概述ispXP2芯片介绍FPGA与CPLD的比较VrilogHDL编程语言编程实例ispLEVER7.0开发环境作业:数字时钟10/21/24全国大学生电子设计竞赛----FPGA培训3可编程逻辑器件概述PLD的发展历程:10/21/24全国大学生电子设计竞赛----FPGA培训4PLD的分类按集成度分类:10/21/24全国大学生电子设计竞赛----FPGA培训5按结构分类乘积项结构:大部分简单PLD和CPLD查找表结构:大多数FPGA按编程工艺分类熔丝(Fuse)型反熔丝(Anti-fuse)型EPROM型,紫外线擦除电可编程逻辑器件EEPROM型SRAM型:大部分FPGA器件采用此种编程工艺Flash型10/21/24全国大学生电子设计竞赛----FPGA培训6简单PLD器件被取代的原因阵列规模小,资源不够用于设计数字系统片内寄存器资源不足,难以构成丰富的时序电路I/O不够灵活编程不便,需专用的编程工具10/21/24全国大学生电子设计竞赛----FPGA培训7FPGA/CPLD被广泛采用的原因规模越来越大,单片逻辑门数已愈千万。开发过程投资小。FPGA/CPLD芯片在出厂前都经过了严格的测试,而且设计灵活,发现错误可直接更改设计,减少了投片风险。用FPGA/CPLD试制功能样机,能以最快速度占领市场。有些领域,标准协议发展太快,设计ASIC根不上技术更新速度,只能依靠FPGA/CPLD完成系统研制与开发。FPGA/CPLD开发工具智能化,功能强大。新型FPGA内嵌CPU或DSP内核,支持软硬件协同设计,可作为SOPC硬件平台。10/21/24全国大学生电子设计竞赛----FPGA培训810/21/24全国大学生电子设计竞赛----FPGA培训9XP2基本结构JTAG&SPIPortssysCLOCKPLLsFrequencySynthesis-Upto4perdeviceEnhancedConfigurationLogicincludesDualBoot,Decryption&TransFRPre-EngineeredSourceSynchronousSupport:DDR2–400MbpsGeneric–750MbpsOn-ChipOscillatorFlashFlexiblesysIOBuffers:LVCMOS,HSTL,SSTL,LVDS,++DSPBlocksMultiplyandAccumulateSupportForUpto3218X18MultiplierssysMEMBlockRAM18KbitDualPortUpto885KbitsProgrammableFunctionUnits(PFUs)Upto40KLUTsFlexibleRoutingOptimizedforSpeed,CostandRoutability10/21/24全国大学生电子设计竞赛----FPGA培训10DeviceXP2-5XP2-8XP2-17XP2-30XP2-40LUTs(K)58172940EBRSRAMBlocks912152148EBRSRAM(Kbits)166221276387885DistributedRAM(Kbits)1018355683#18x18Multipliers1216202832PLLs22444Package&IOCombinations132-ballcsBGA(8x8mm)8686144-pinTQFP(20x20mm)100100208-pinPQFP(28x28mm)146146146256-ballftBGA(17x17mm)172201201201484-ballfpBGA(23x23mm)358363363672-ballfpBGA(27x27mm)472540查找表(Look-Up-Table)简称为LUT,LUT本质上就是一个RAM。它把数据事先写入RAM后,每当输入一个信号就等于输入一个地址进行查表,找出地址对应的内容,然后输出。10/21/24全国大学生电子设计竞赛----FPGA培训11FPGA/CPLD比较10/21/24全国大学生电子设计竞赛----FPGA培训12什么是VerilogHDL?VerilogHDL是一种硬件描述语言,用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模。被建模的数字系统对象的复杂性可以介于简单的门和完整的电子数字系统之间。数字系统能够按层次描述,并可在相同描述中显式地进行时序建模。VerilogHDL语言提供了编程语言接口,通过该接口可以在模拟、验证期间从设计外部访问设计,包括模拟的具体控制和运行。VerilogHDL语言不仅定义了语法,而且对每个语法结构都定义了清晰的模拟、仿真语义。因此,用这种语言编写的模型能够使用Verilog仿真器进行验证。语言从C编程语言中继承了多种操作符和结构。VerilogHDL语言的核心子集非常易于学习和使用,完整的硬件描述语言足以对从最复杂的芯片到完整的电子系统进行描述。Verilog–“TellmehowyourcircuitshouldbehaveandIwillgiveyouthehardwarethatdoesthejob.”10/21/24全国大学生电子设计竞赛----FPGA培训13功能模块:10/21/24全国大学生电子设计竞赛----FPGA培训14结构模块:10/21/24...