数字系统设计与VerilogHDL(第7版)第3章QuartusPrime使用指南3

1QuartusPrime原理图设计3

2基于IP核的设计3

3SignalTapII的使用方法3

4QuartusPrime的优化设置与时序分析3

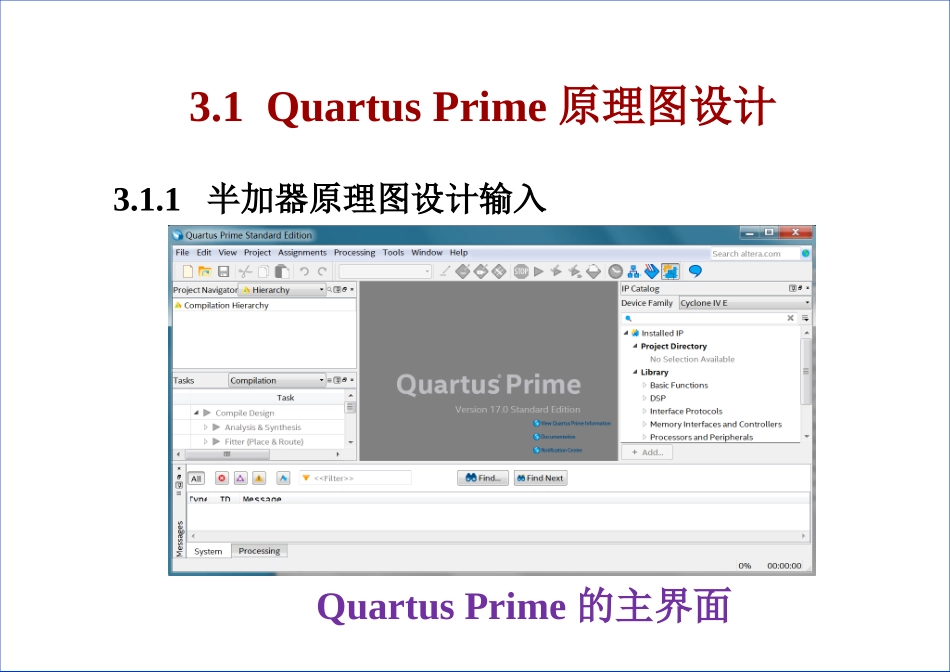

1QuartusPrime原理图设计3

1半加器原理图设计输入QuartusPrime的主界面QuartusPrime的主界面3

1半加器原理图设计输入QuartusPrime的主界面输入元件3

1半加器原理图设计输入QuartusPrime的主界面半加器电路图3

1半加器原理图设计输入QuartusPrime的主界面使用NewProjectWizard创建工程3

1半加器原理图设计输入QuartusPrime的主界面设置Directory,Name,Top-LevelEntity对话框3

1半加器原理图设计输入QuartusPrime的主界面将设计文件加入当前工程中3

1半加器原理图设计输入QuartusPrime的主界面选择目标器件3

1半加器原理图设计输入QuartusPrime的主界面选择综合器、仿真器3

1半加器原理图设计输入QuartusPrime的主界面工程信息汇总显示3

21位全加器设计输入QuartusPrime的主界面创建元件符号对话框3

21位全加器设计输入QuartusPrime的主界面1位全加器原理图3

31位全加器的编译QuartusPrime的主界面选择菜单Processing→StartCompilation,或者单击按钮,即启动了完全编译,完全编译包括如下5个过程:分析与综合(Analysis&Synthesis);适配(Fitter);装配(Assembler);定时分析(TimeQuestTimingAnalysis);网表文件提取(