CameraLink 图像采集接口电路1.Camera Link 标准概述Camera Link 技术标准是基于 National Semiconductor 公司的 Channel Link 标准发展而来的,而 Channel Link 标准是一种多路并行 LVDS 传输接口标准

低压差分信号( LVDS )是一种低摆幅的差分信号技术,电压摆幅在 350mV 左右,具有扰动小,跳变速率快的特点,在无失传输介质里的理论最大传输速率在 1

923Gbps

90年代美国国家半导体公司( National Semiconductor )为了找到平板显示技术的解决方案,开发了基于 LVDS 物理层平台的 Channel Link 技术

此技术一诞生就被进行了扩展,用来作为新的通用视频数据传输技术使用

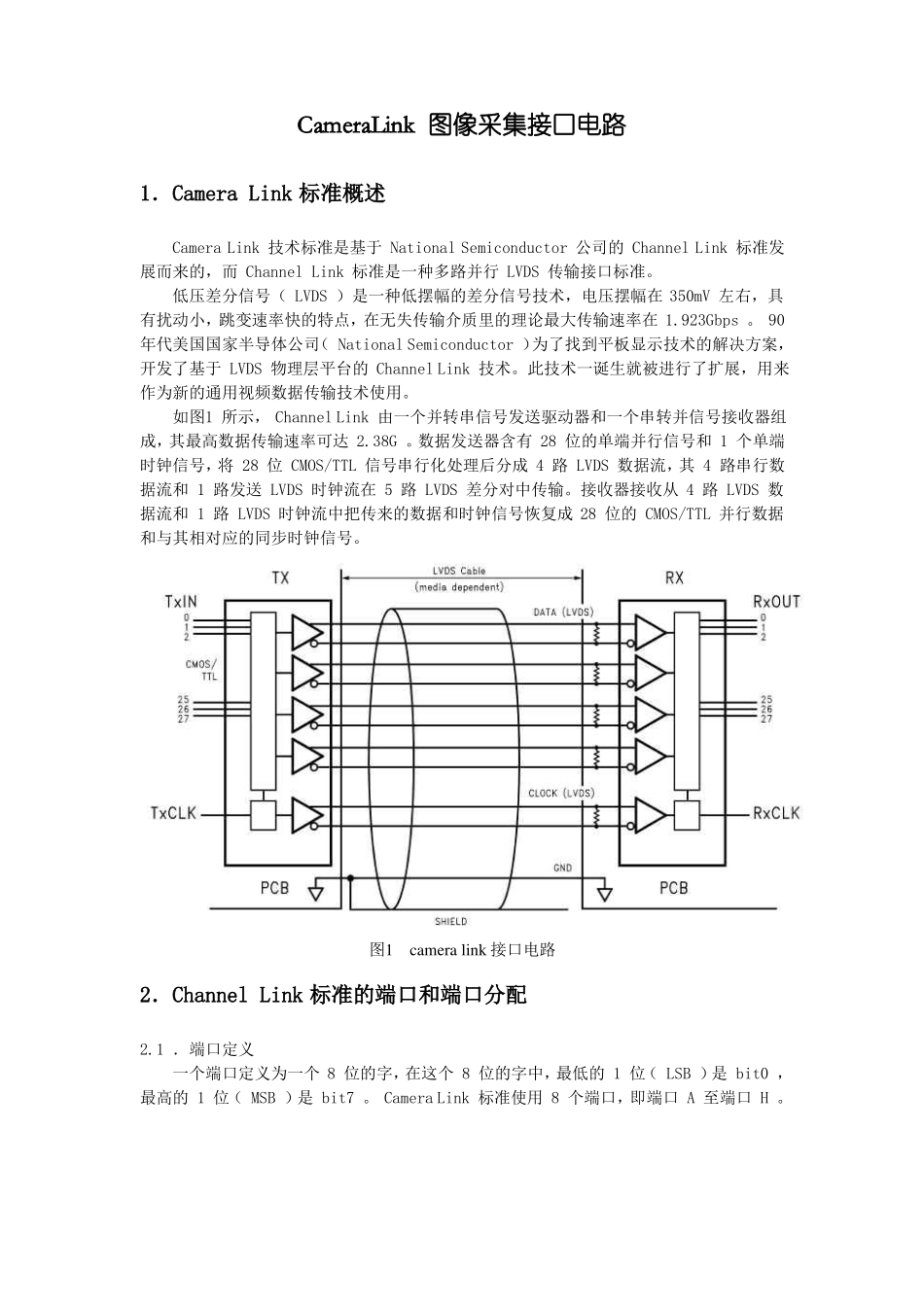

如图1 所示, Channel Link 由一个并转串信号发送驱动器和一个串转并信号接收器组成,其最高数据传输速率可达 2

数据发送器含有 28 位的单端并行信号和 1 个单端时钟信号,将 28 位 CMOS/TTL 信号串行化处理后分成 4 路 LVDS 数据流,其 4 路串行数据流和 1 路发送 LVDS 时钟流在 5 路 LVDS 差分对中传输

接收器接收从 4 路 LVDS 数据流和 1 路 LVDS 时钟流中把传来的数据和时钟信号恢复成 28 位的 CMOS/TTL 并行数据和与其相对应的同步时钟信号

图1camera link 接口电路2.Channel Link 标准的端口和端口分配2

1 .端口定义一个端口定义为一个 8 位的字,在这个 8 位的字中,最低的 1 位( LSB )是 bit0 ,最高的 1 位( MSB )是 bit7

Camera Link 标准使用 8 个端口,即端口 A 至端口 H

2 .端口分配在基本配置模式中,端口 A