89C52 单片机模块 1 概述 1

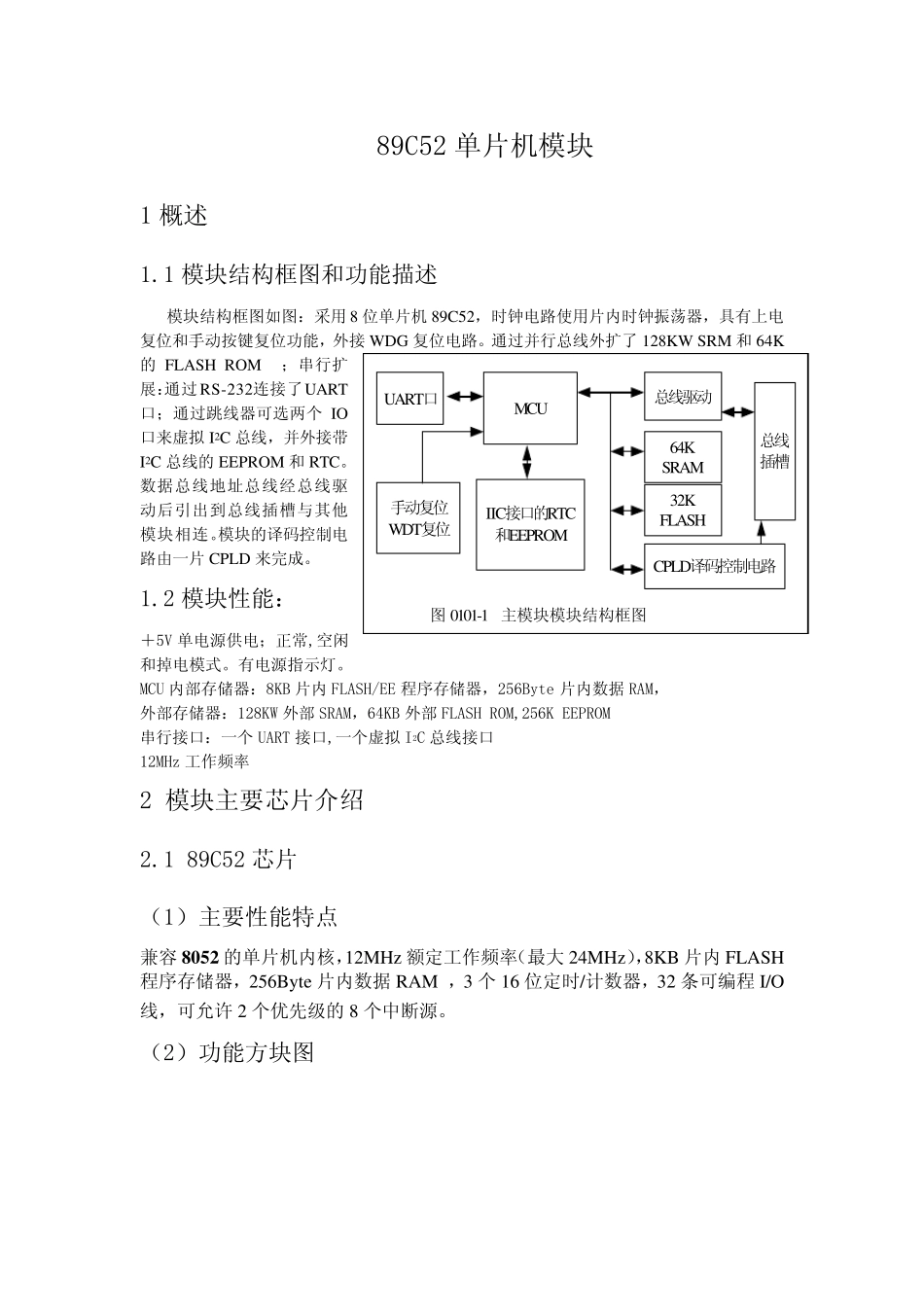

1 模块结构框图和功能描述 模块结构框图如图:采用8 位单片机89C52,时钟电路使用片内时钟振荡器,具有上电复位和手动按键复位功能,外接WDG 复位电路

通过并行总线外扩了 128KW SRM 和64K的 FLASH ROM;串行扩展:通过 RS-232连接了UART口;通过跳线器可选两个 IO口来虚拟 I2C 总线,并外接带I2C 总线的 EEPROM 和RTC

数据总线地址总线经总线驱动后引出到总线插槽与其他模块相连

模块的译码控制电路由一片CPLD 来完成

2 模块性能: +5V 单电源供电;正常,空闲和掉电模式

有电源指示灯

MCU 内部存储器:8KB 片内FLASH/EE 程序存储器,256Byte 片内数据 RAM, 外部存储器:128KW 外部 SRAM,64KB 外部 FLASH ROM,256K EEPROM 串行接口:一个 UART 接口,一个虚拟 I2C 总线接口 12MHz 工作频率 2 模块主要芯片介绍 2

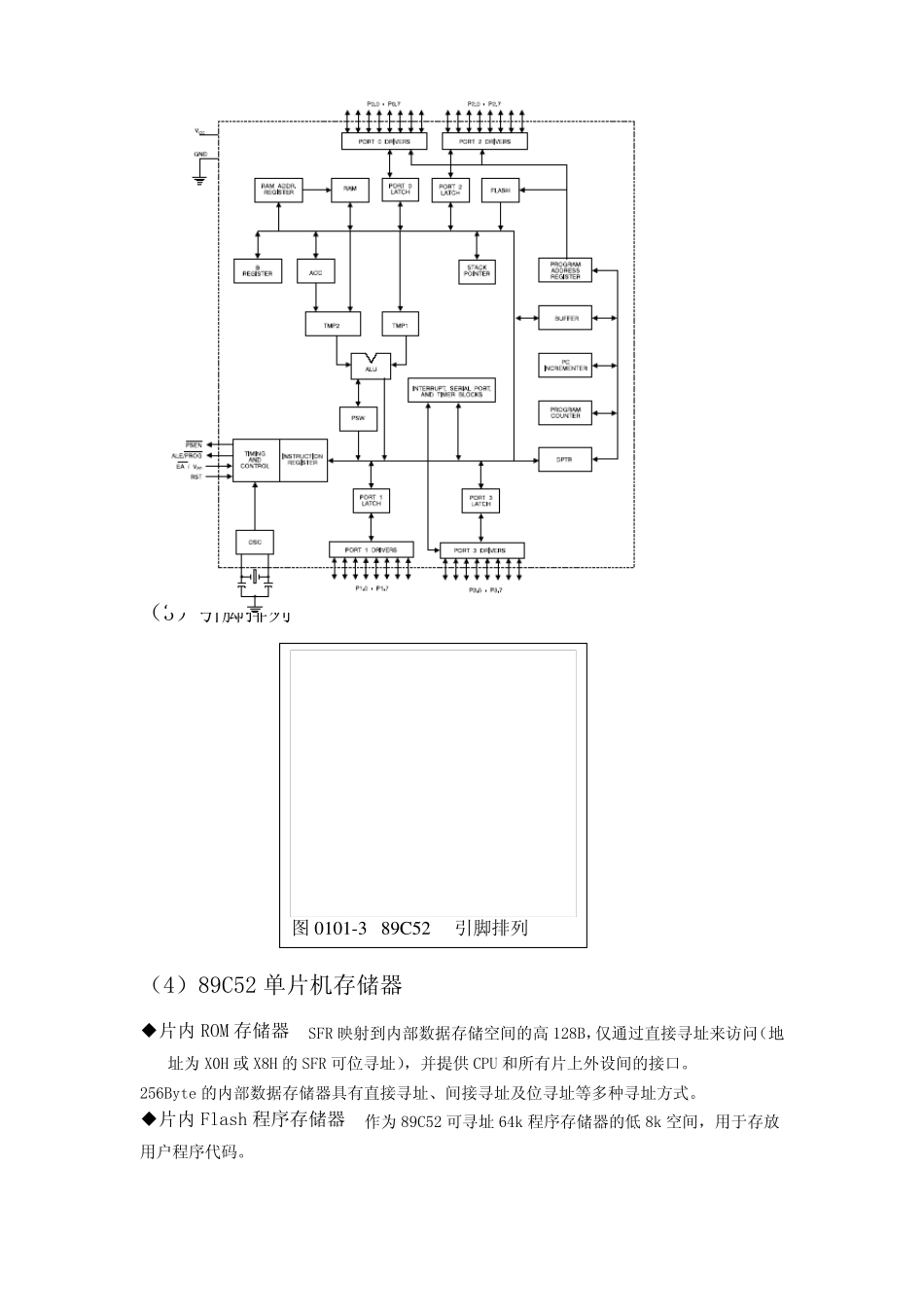

1 89C52 芯片 (1)主要性能特点 兼容 8052 的单片机内核,12MHz 额定工作频率(最大 24MHz),8KB 片内FLASH程序存储器,256Byte 片内数据 RAM ,3 个 16 位定时/计数器,32 条可编程 I/O线,可允许 2 个优先级的 8 个中断源

(2)功能方块图 UART口手动复位WDT复位MCU总线驱动64K SRAM32KFLASHIIC接口的RTC和EEPROM总线插槽CPLD译码控制电路 图0101-1 主模块模块结构框图 图0101-2 89C 52结构框图 (3)引脚排列 (4)89C52 单片机存储器 ◆片内 ROM 存储器 SFR 映射到内部数据存储空间的高 128B,仅通过直接寻址来访问(地址为 X0H 或 X8H 的 SFR 可位寻址),并