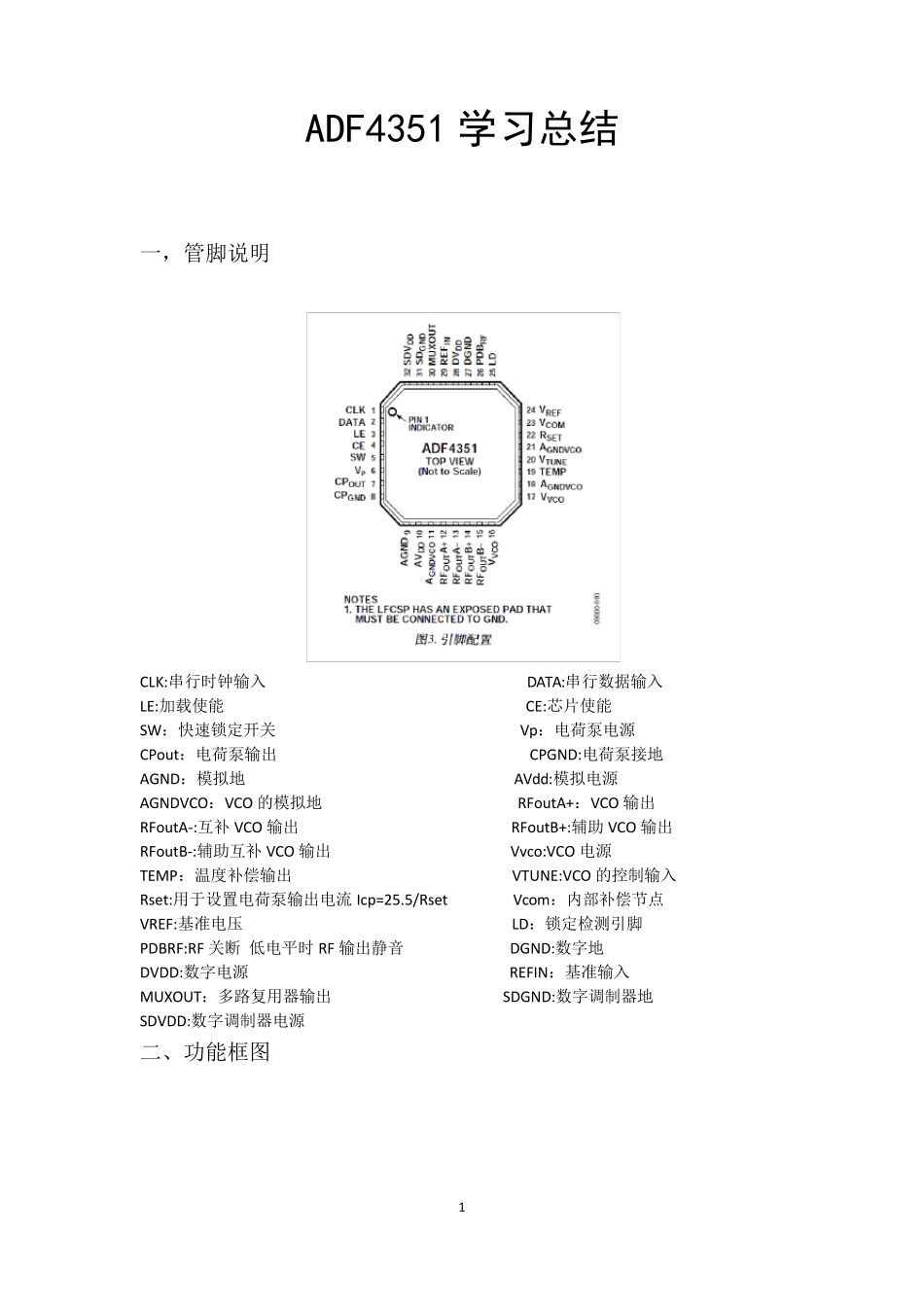

1 ADF4351 学习总结 一,管脚说明 CLK:串行时钟输入 DATA:串行数据输入 LE:加载使能 CE:芯片使能 SW:快速锁定开关 Vp:电荷泵电源 CPout:电荷泵输出 CPGND:电荷泵接地 AGND:模拟地 AVdd:模拟电源 AGNDVCO:VCO 的模拟地 RFoutA+:VCO 输出 RFoutA-:互补VCO 输出 RFoutB+:辅助VCO 输出 RFoutB-:辅助互补VCO 输出 Vvco:VCO 电源 TEMP:温度补偿输出 VTUNE:VCO 的控制输入 Rset:用于设置电荷泵输出电流Icp=25

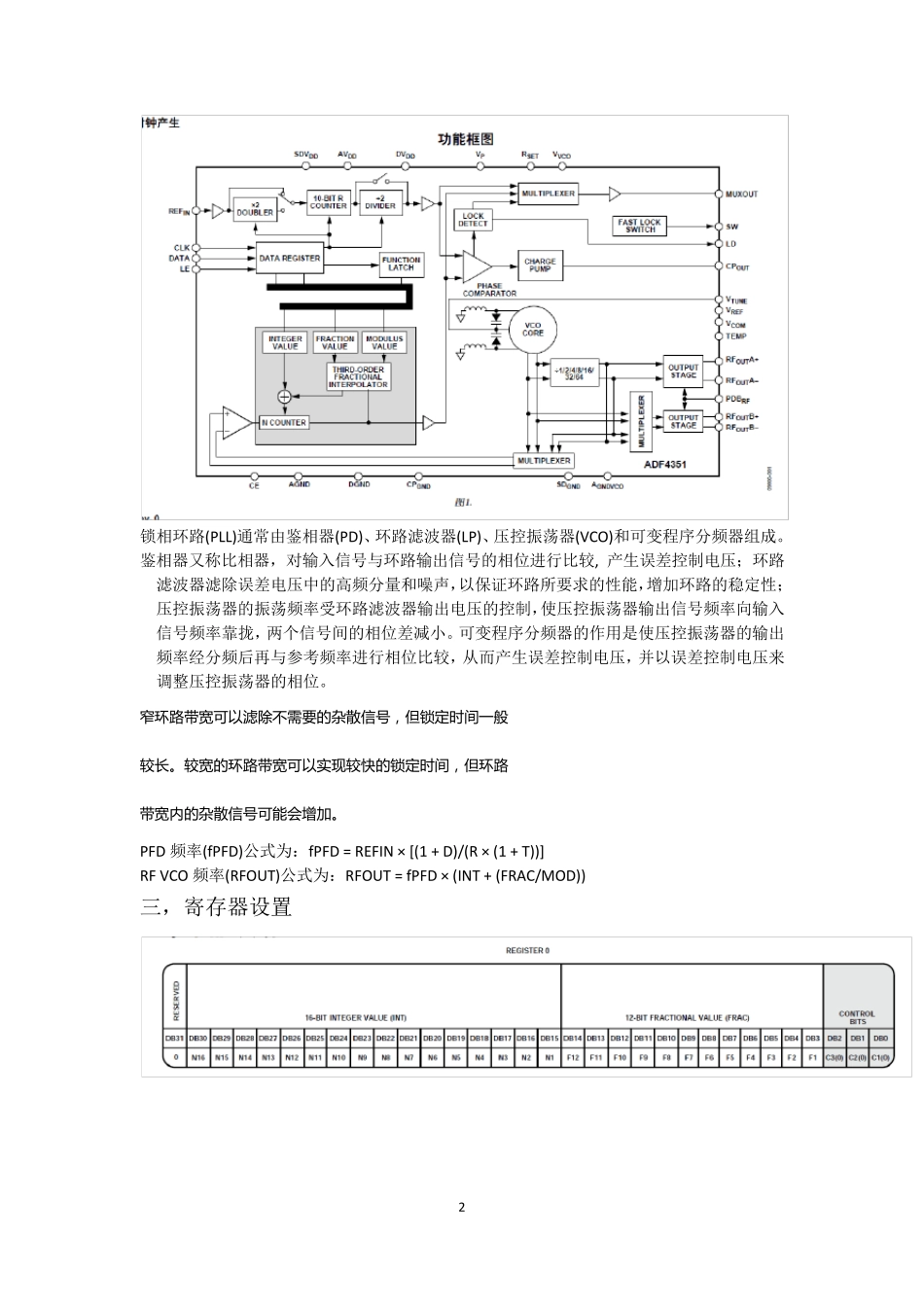

5/Rset Vcom:内部补偿节点 VREF:基准电压 LD:锁定检测引脚 PDBRF:RF 关断 低电平时RF 输出静音 DGND:数字地 DVDD:数字电源 REFIN:基准输入 MUXOUT:多路复用器输出 SDGND:数字调制器地 SDVDD:数字调制器电源 二、功能框图 2 锁相环路(PLL)通常由鉴相器(PD)、环路滤波器(LP)、压控振荡器(VCO)和可变程序分频器组成

鉴相器又称比相器,对输入信号与环路输出信号的相位进行比较, 产生误差控制电压;环路滤波器滤除误差电压中的高频分量和噪声,以保证环路所要求的性能,增加环路的稳定性;压控振荡器的振荡频率受环路滤波器输出电压的控制,使压控振荡器输出信号频率向输入信号频率靠拢,两个信号间的相位差减小

可变程序分频器的作用是使压控振荡器的输出频率经分频后再与参考频率进行相位比较,从而产生误差控制电压,并以误差控制电压来调整压控振荡器的相位

窄 环 路 带 宽 可 以 滤 除 不 需 要 的 杂 散 信 号 , 但 锁 定 时 间 一 般 较 长

较 宽 的 环 路 带 宽 可 以 实现较 快的 锁 定 时 间 , 但 环 路 带 宽 内的 杂 散 信 号 可 能会增加