Allegro 16

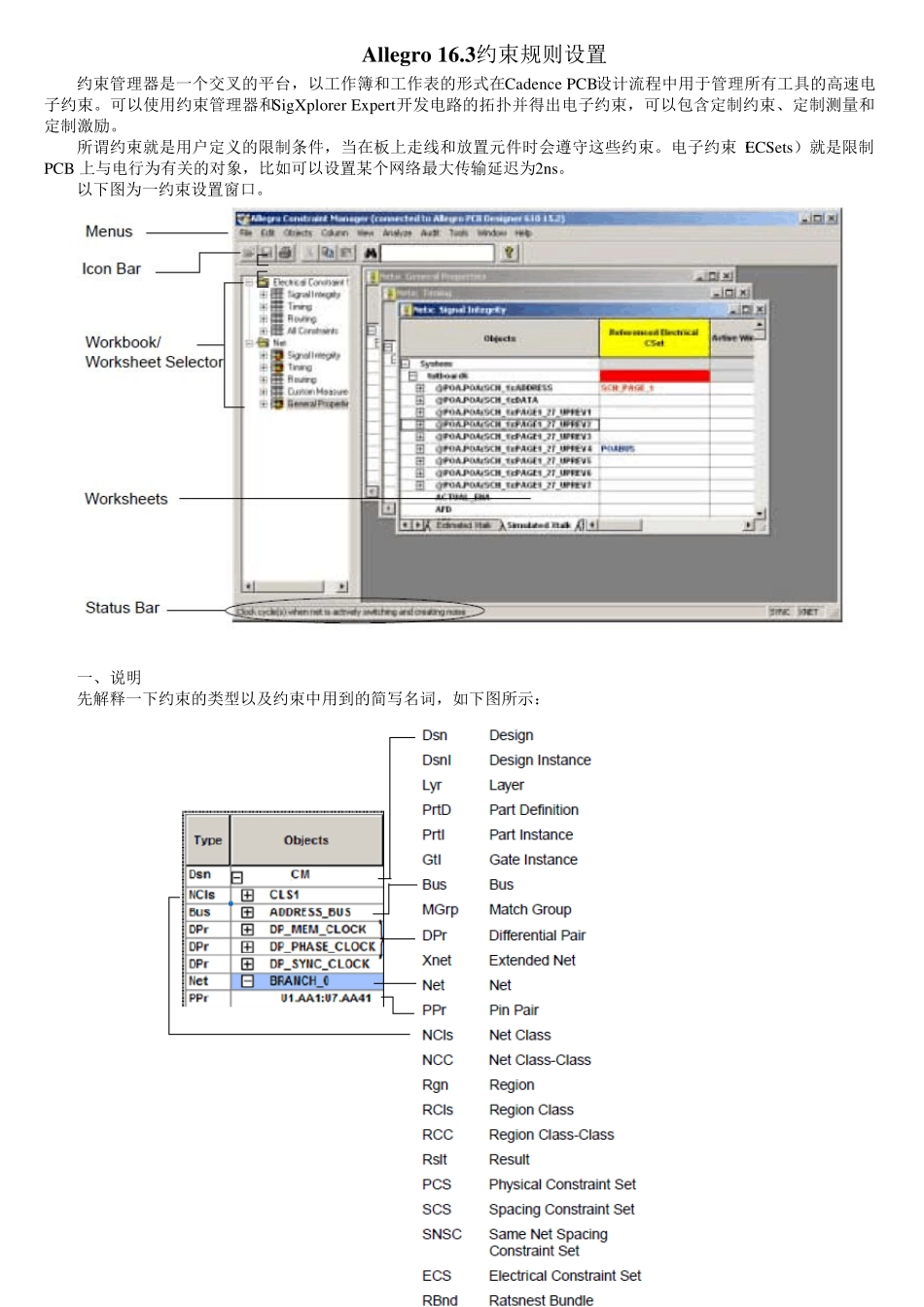

3约束规则设置 约束管理器是一个交叉的平台,以工作簿和工作表的形式在 Cadence PCB设计流程中用于管理所有工具的高速电子约束

可以使用约束管理器和SigXplorer Ex pert 开发电路的拓扑并得出电子约束,可以包含定制约束、定制测量和定制激励

所谓约束就是用户定义的限制条件,当在板上走线和放置元件时会遵守这些约束

电子约束(ECSets)就是限制PCB 上与电行为有关的对象,比如可以设置某个网络最大传输延迟为2ns

以下图为一约束设置窗口

一、说明 先解释一下约束的类型以及约束中用到的简写名词,如下图所示: 1、 NCIs(NET CLASS) 由众多nets或者bu ses、differential pairs、Xnet所组成的类,可对其赋予相似的约束

2 、NCC(Net Class-Class) 一般用在约束组与组之间的间距的时候使用,如下图

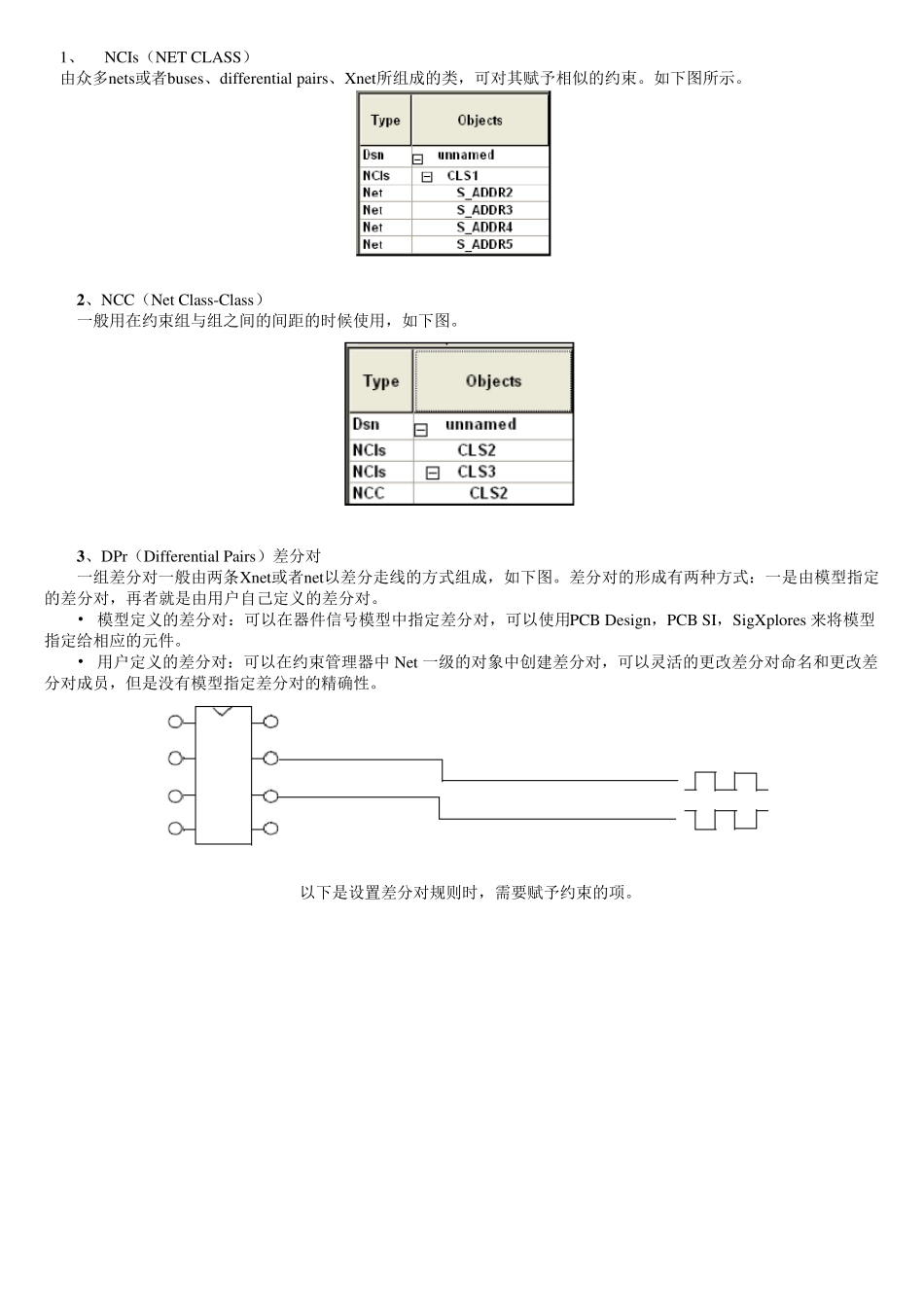

3 、DPr(Differential Pairs)差分对 一组差分对一般由两条Xnet或者net以差分走线的方式组成,如下图

差分对的形成有两种方式:一是由模型指定的差分对,再者就是由用户自己定义的差分对

• 模型定义的差分对:可以在器 件 信 号 模型中 指定差分对,可以使用PCB Design,PCB SI,SigXplores 来 将 模型指定给 相应 的元 件

• 用户定义的差分对:可以在约束管 理 器 中 Net 一级 的对象 中 创 建 差分对,可以灵 活 的更 改 差分对命 名 和 更 改 差分对成员 ,但 是没 有模型指定差分对的精 确 性

以下是设 置 差分对规 则 时,需 要 赋予约束的项

针对以上约束中用到的一些约束点进行解释说明: 差分对的worksheets包含5个主要的约束目录: (1)Pin Delay 此值指一对网络之间管