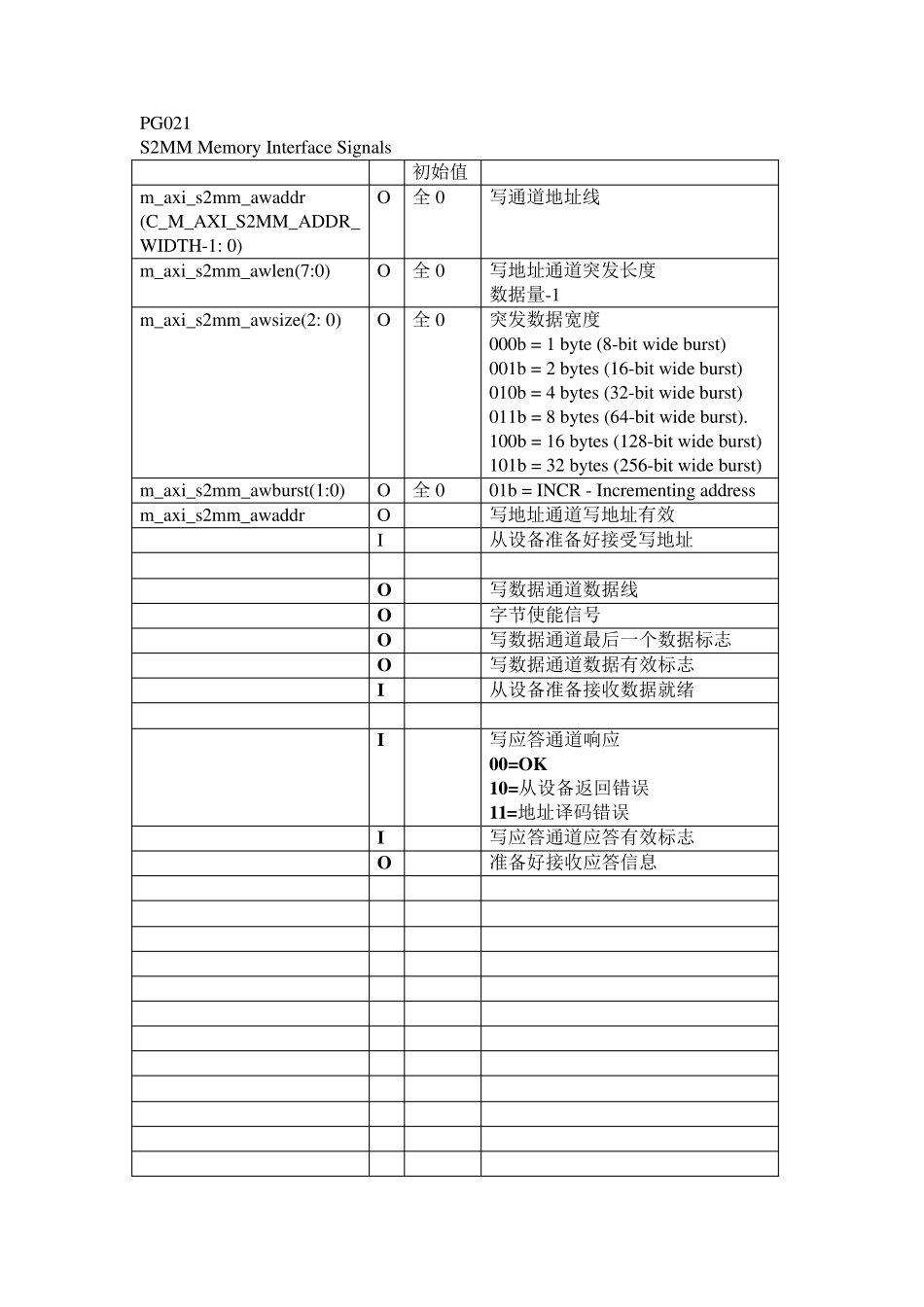

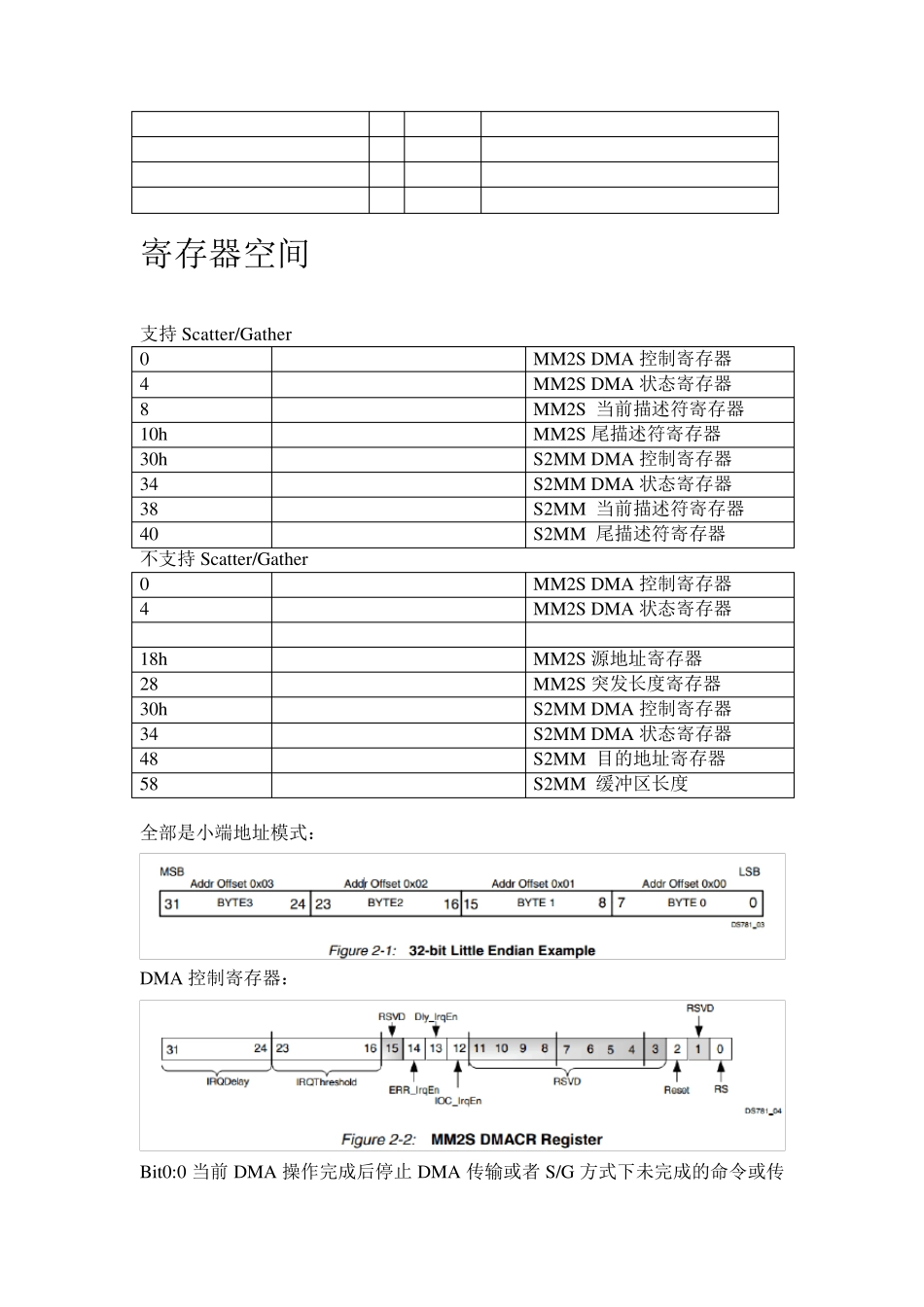

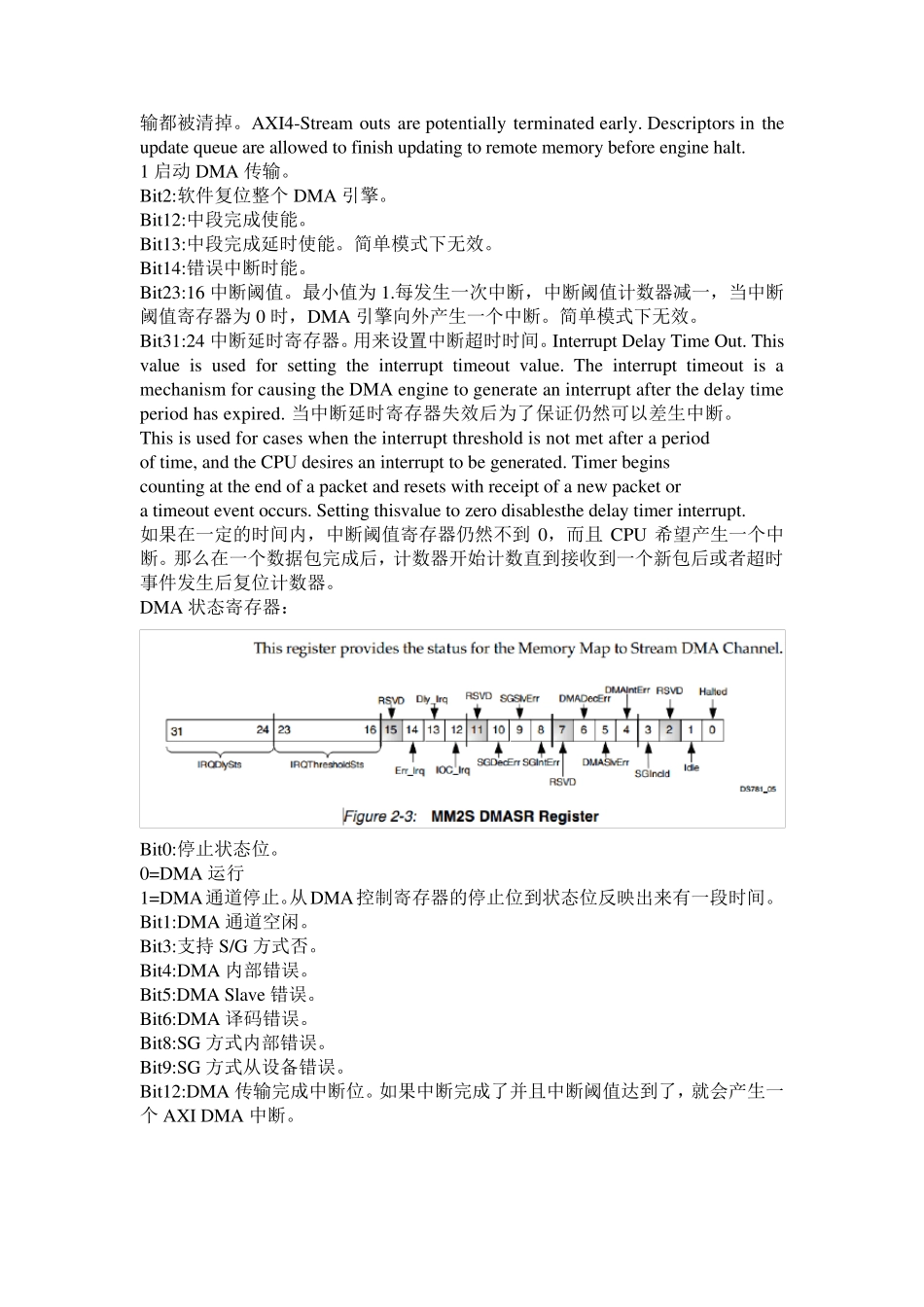

PG021 S2MM Memory Interface Signals 初始值 m_axi_s2mm_awaddr (C_M_AXI_S2MM_ADDR_ WIDTH-1: 0) O 全0 写通道地址线 m_axi_s2mm_awlen(7:0) O 全0 写地址通道突发长度 数据量-1 m_axi_s2mm_awsize(2: 0) O 全0 突发数据宽度 000b = 1 byte (8-bit wide burst) 001b = 2 bytes (16-bit wide burst) 010b = 4 bytes (32-bit wide burst) 011b = 8 bytes (64-bit wide burst). 100b = 16 bytes (128-bit wide burst) 101b = 32 bytes (256-bit wide burst) m_axi_s2mm_awburst(1:0) O 全0 01b = INCR - Incrementing address m_axi_s2mm_awaddr O 写地址通道写地址有效 I 从设备准备好接受写地址 O 写数据通道数据线 O 字节使能信号 O 写数据通道最后一个数据标志 O 写数据通道数据有效标志 I 从设备准备接收数据就绪 I 写应答通道响应 00=O K 10=从设备返回错误 11=地址译码错误 I 写应答通道应答有效标志 O 准备好接收应答信息 寄存器空间 支持Scatter/Gather 0 MM2S DMA 控制寄存器 4 MM2S DMA 状态寄存器 8 MM2S 当前描述符寄存器 10h MM2S 尾描述符寄存器 30h S2MM DMA 控制寄存器 34 S2MM DMA 状态寄存器 38 S2MM 当前描述符寄存器 40 S2MM 尾描述符寄存器 不支持Scatter/Gather 0 MM2S DMA 控制寄存器 4 MM2S DMA 状态寄存器 18h MM2S 源地址寄存器 28 MM2S 突发长度寄存器 30h S2MM DMA 控制寄存器 34 S2MM DMA 状态寄存器 48 S2MM 目的地址寄存器 58 S2MM 缓冲区长度 全部是小端地址模式: DMA 控制寄存器: Bit0:0 当前DMA 操作完成后停止DMA 传输或者S/G 方式下未完成的命令或传输都被清掉。AXI4-Stream outs are potentially terminated early. Descriptors in the update queue are allowed to finish updating to remote memory before engine halt. 1 启动 DMA 传输。 Bit2:软件复位整个 DMA 引擎。 Bit12:中段完成使能。 Bit13:中段完成延时使能。简单模式下无效。 Bit14:错误中断时能。 Bit23:16 中断阈值。最小值为 1.每发生一次中断,中断阈值计数器减一,当中断阈值寄存器为 0 时,DMA 引擎向外产生一个中断。简单模式下无效。 Bit31:24 中断延时寄存器。用来设置中断超时时间。Interrupt Delay Time Out...