实验六 CV SD 编码器和 CV SD 译码器系统 一、实验原理和电路说明 CVSD 编码系统分别由 CVSD 发送模块和 CVSD 译码模块模块完成

CVSD编码器模块将模拟信号进行 CVSD 编码,转换为数字信号在信道上进行传输

CVSD 译码器模块将信道上接收到的数字信号进行 CVSD 码字译码处理,还原出模拟信号

CVSD 编译码器使用了莫托洛拉公司生产的大规模集成电路 MC34115芯片,该芯片可用于 CVSD 编码,又可用作 CVSD 解码,其取决于芯片第 15 脚的使能信号:“1”电平为编码方式,“0”电平为译码方式

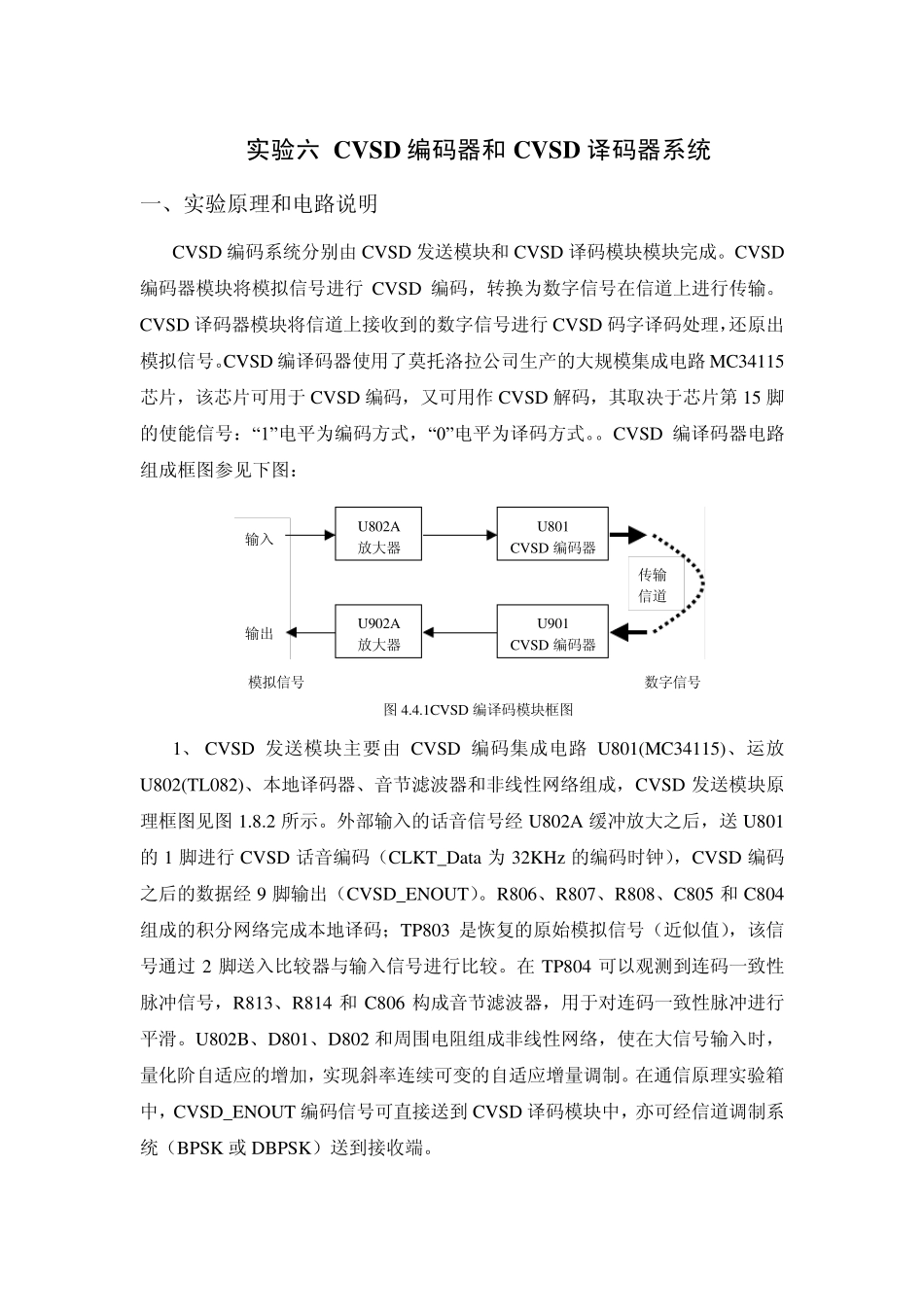

CVSD 编译码器电路组成框图参见下图: 图 4

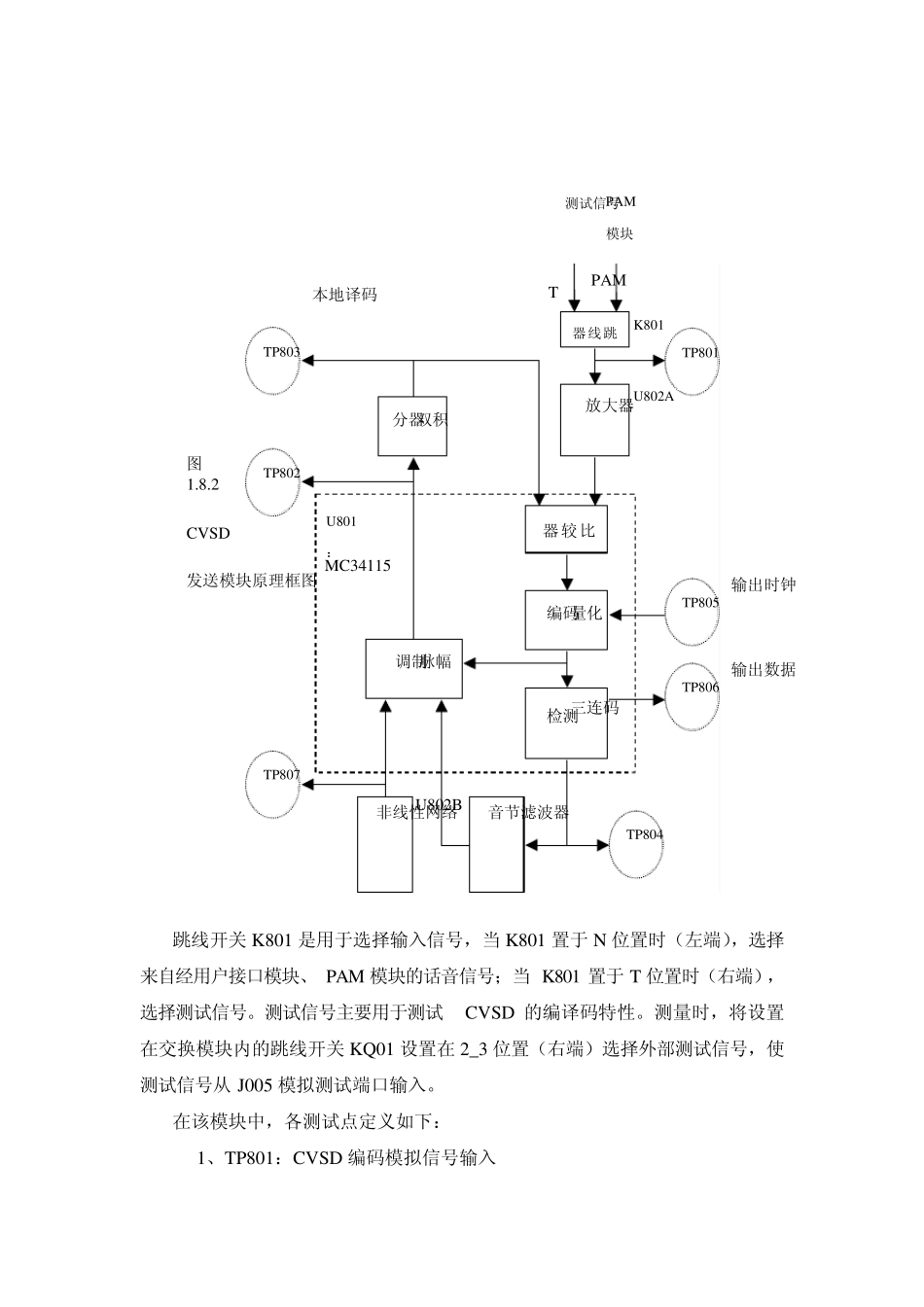

1CVSD 编译码模块框图输入输出U802A放大器U801CVSD 编码器U902A放大器U901CVSD 编码器传输信道模拟信号数字信号 1、 CVSD 发送模块主要由 CVSD 编码集成电路 U801(MC34115)、运放U802(TL082)、本地译码器、音节滤波器和非线性网络组成,CVSD 发送模块原理框图见图 1

外部输入的话音信号经 U802A 缓冲放大之后,送 U801的 1 脚进行 CVSD 话音编码(CLKT_Data 为 32KHz 的编码时钟),CVSD 编码之后的数据经 9 脚输出(CVSD_ENOUT)

R806、R807、R808、C805 和 C804组成的积分网络完成本地译码;TP803 是恢复的原始模拟信号(近似值),该信号通过 2 脚送入比较器与输入信号进行比较

在 TP804 可以观测到连码一致性脉冲信号,R813、R814 和 C806 构成音节滤波器,用于对连码一致性脉冲进行平滑

U802B、D801、D802 和周围电阻组成非线性网络,使在大信号输入时,量化阶自适应的增加,实现斜率连续可变的自适应增量调制

在通信原理实验箱中,CV