ALLEGRO 约束规则设置步骤(以 DDR 为例) Dyyxh@pcbtech tzyhust@163

com 本文是我对约束规则设置方面的一些理解,希望对新手能有所帮助

由于本人水平有限,错误之处难免,希望大家不吝赐教

在进行高速布线时,一般都需要进行线长匹配,这时我们就需要设置好 constraint 规则,并将这些规则分配到各类 net grou p 上

下面以 ddr 为例,具体说明这些约束设置的具体步骤

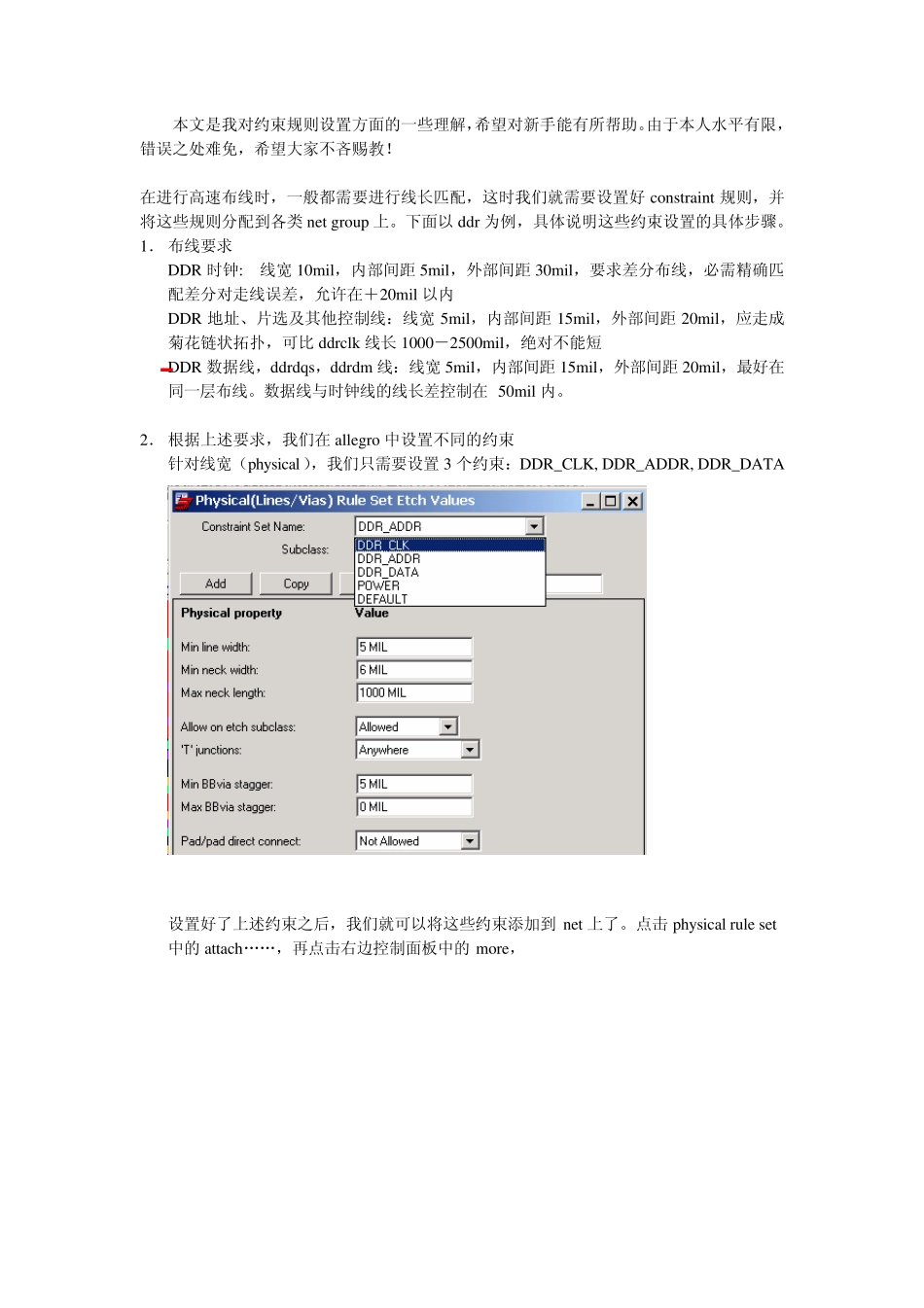

1. 布线要求 DDR 时钟: 线宽 10mil,内部间距 5mil,外部间距 30mil,要求差分布线,必需精确匹配差分对走线误差,允许在+20mil 以内 DDR 地址、片选及其他控制线:线宽 5mil,内部间距 15mil,外部间距 20mil,应走成菊花链状拓扑,可比 ddrclk 线长 1000-2500mil,绝对不能短 DDR 数据线,ddrdqs,ddrdm 线:线宽 5mil,内部间距 15mil,外部间距 20mil,最好在同一层布线

数据线与时钟线的线长差控制在 50mil 内

2. 根据上述要求,我们在 allegro 中设置不同的约束 针对线宽(phy sical),我们只需要设置 3 个约束:DDR_CLK, DDR_ADDR, DDR_DATA 设置好了上述约束之后,我们就可以将这些约束添加到 net 上了

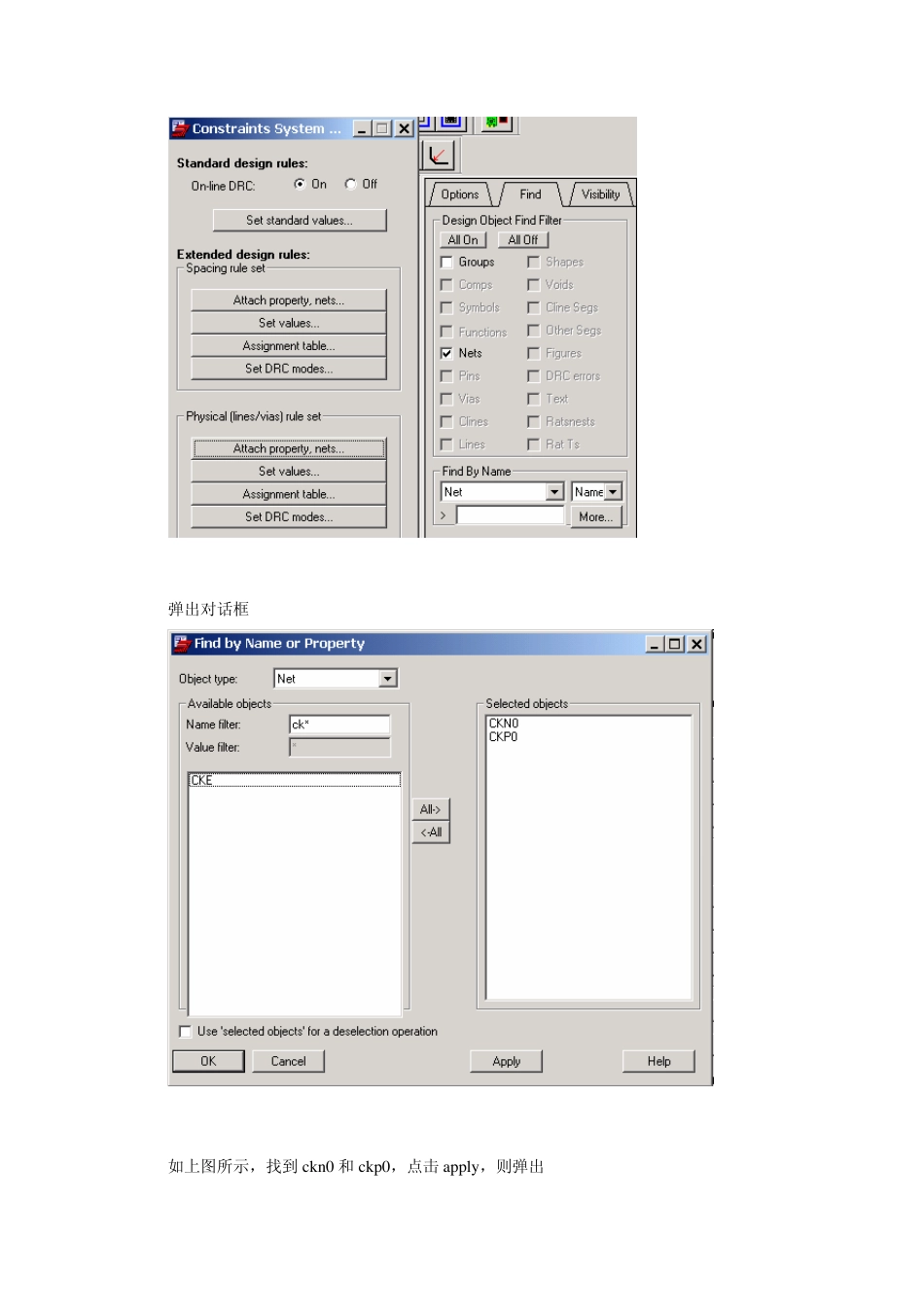

点击phy sical ru le set中的 attach……,再点击右边控制面板中的 more, 弹出对话框 如上图所示,找到 ckn 0 和 ckp 0,点击 ap p ly ,则弹出 选中左边列表中的NET_PHYSICAL_TYPE, 在右边空格内输入DDR_CLK, 点击apply ,弹出 即这两个net 已经添加上了NET_PHYSICAL_TYPE 属性,且值为DDR_CLK

类似的,可以将DDR 数据线