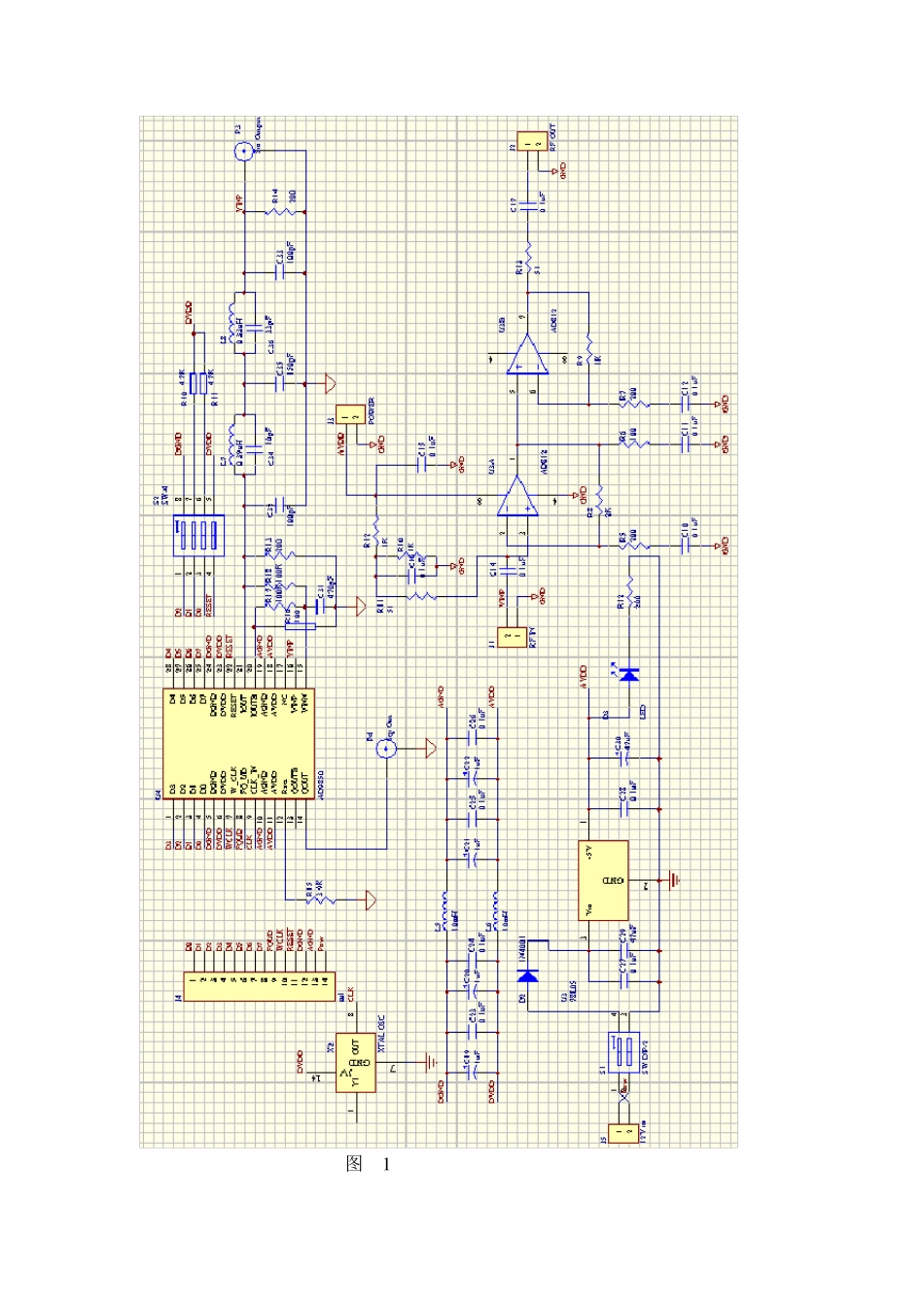

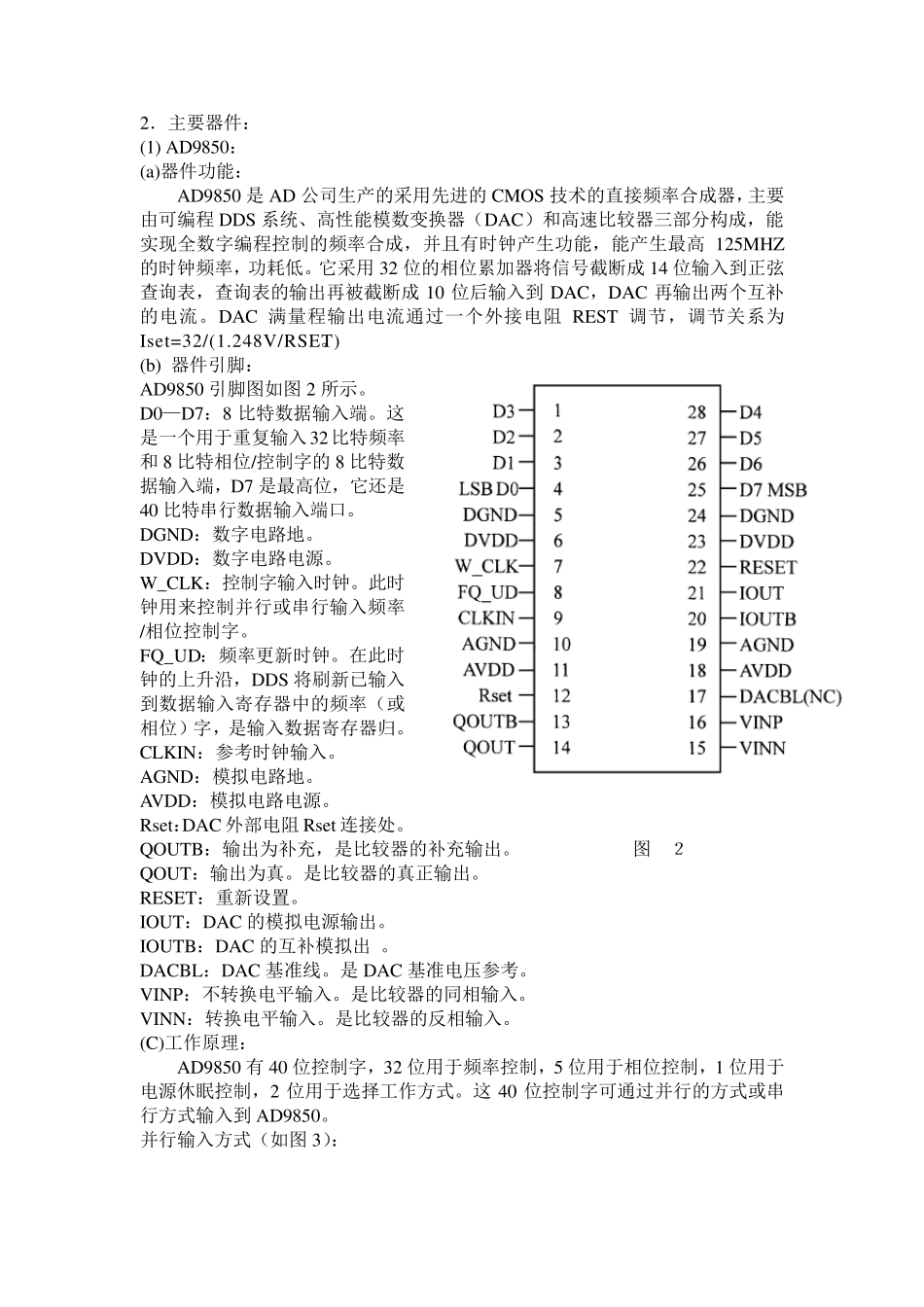

DDS 1.模块功能: DDS 模块主要采用AD9850、AD812、125MHz有源晶振等器件,DDS 是新一代的信号产生方式,它把一系列数字量形式的信号通过 DAC 转换成模拟量形式的信息。它的工作方式是利用高速存储器作查询表,然后通过高速 DAC 产生已经用数字形式存入的波形。与其他频率合成方法相比,DDS 具有频率转换时间短、频率分辨率高、输出相位连续、可编程、全数字化仪与集成等突出优点。 本模块原理图见图 1。 图 1 2.主要器件: (1) AD9850: (a)器件功能: AD9850 是AD 公司生产的采用先进的CMOS 技术的直接频率合成器,主要由可编程DDS 系统、高性能模数变换器(DAC)和高速比较器三部分构成,能实现全数字编程控制的频率合成,并且有时钟产生功能,能产生最高125MHZ的时钟频率,功耗低。它采用32 位的相位累加器将信号截断成14 位输入到正弦查询表,查询表的输出再被截断成10 位后输入到DAC,DAC 再输出两个互补的电流。DAC 满量程输出电流通过一个外接电阻REST 调节,调节关系为Iset=32/(1.248V/RSET)。 (b) 器件引脚: AD9850 引脚图如图2 所示。 D0—D7:8 比特数据输入端。这是一个用于重复输入32比特频率和8 比特相位/控制字的8 比特数据输入端,D7 是最高位,它还是40 比特串行数据输入端口。 DGND:数字电路地。 DVDD:数字电路电源。 W_CLK:控制字输入时钟。此时钟用来控制并行或串行输入频率/相位控制字。 FQ_UD:频率更新时钟。在此时钟的上升沿,DDS 将刷新已输入到数据输入寄存器中的频率(或相位)字,是输入数据寄存器归。 CLKIN:参考时钟输入。 AGND:模拟电路地。 AVDD:模拟电路电源。 Rset:DAC 外部电阻Rset连接处。 QOUTB:输出为补充,是比较器的补充输出。 图 2 QOUT:输出为真。是比较器的真正输出。 RESET:重新设置。 IOUT:DAC 的模拟电源输出。 IOUTB:DAC 的互补模拟出 。 DACBL:DAC 基准线。是DAC 基准电压参考。 VINP:不转换电平输入。是比较器的同相输入。 VINN:转换电平输入。是比较器的反相输入。 (C)工作 原 理 : AD9850 有40 位控制字,32 位用于频率控制,5 位用于相位控制,1 位用于电源休 眠 控制,2 位用于选 择 工作 方 式 。这 40 位控制字可通过并行的方 式 或串行方 式 输入到AD9850。 并行输入方 式 (如图3): 图3 AD9850 并行输入工作时序图 在并行装入方式中,通过8 位总线D0—D7 可...