4 第二章 Design Compiler 概述 Design Compiler 是Synopsys 综合软件的核心产品

它提供约束驱动时序最优化,并支持众多的设计类型,把设计者的HDL 描述综合成与工艺相关的门级设计;它能够从速度、面积和功耗等方面来优化组合电路和时序电路设计,并支持平直或层次化设计

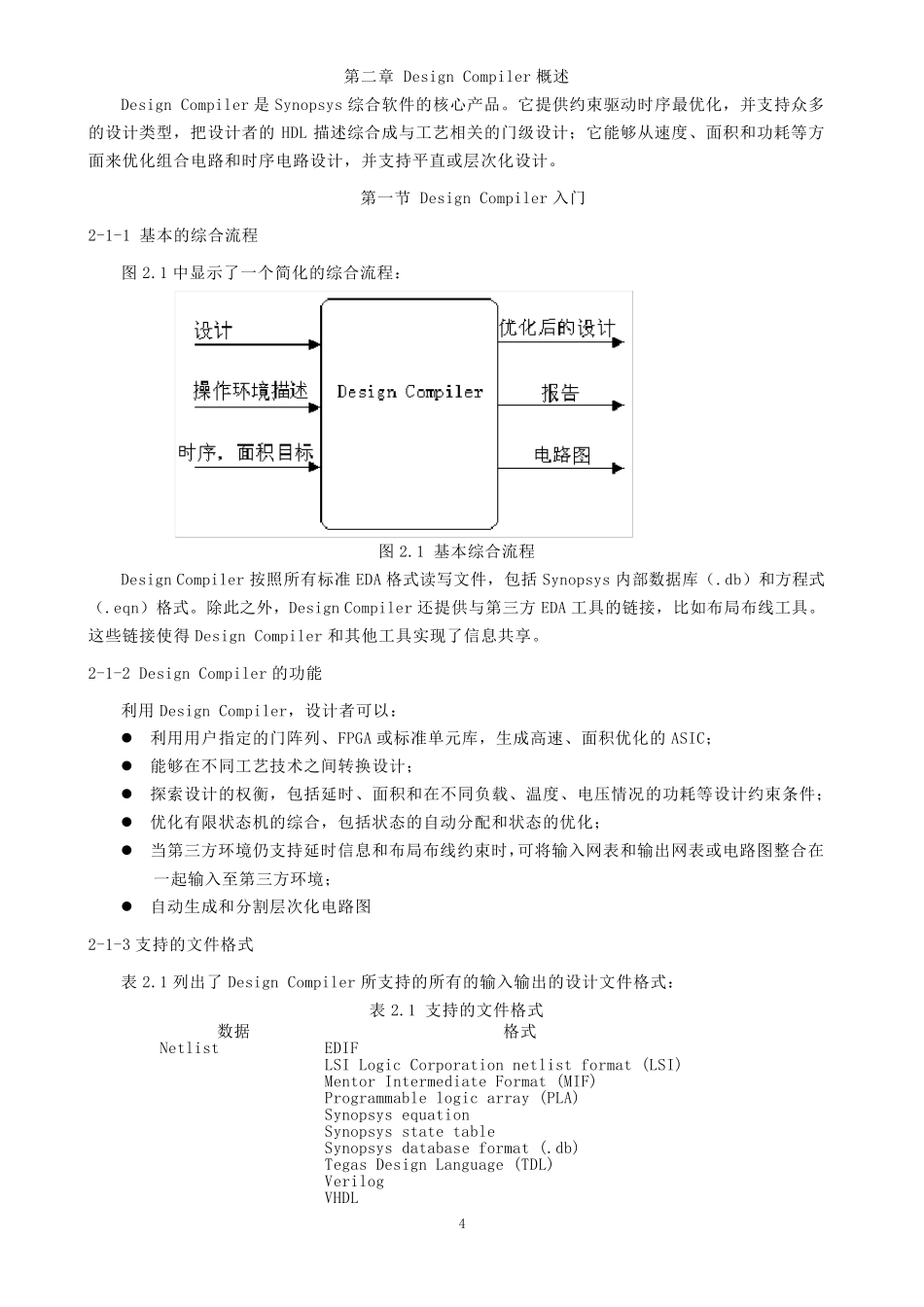

第一节 Design Compiler 入门 2-1-1 基本的综合流程 图 2

1 中显示了一个简化的综合流程: 图 2

1 基本综合流程 Design Compiler 按照所有标准 EDA 格式读写文件,包括 Synopsys 内部数据库(

db)和方程式(

eqn)格式

除此之外,Design Compiler 还提供与第三方 EDA 工具的链接,比如布局布线工具

这些链接使得 Design Compiler 和其他工具实现了信息共享

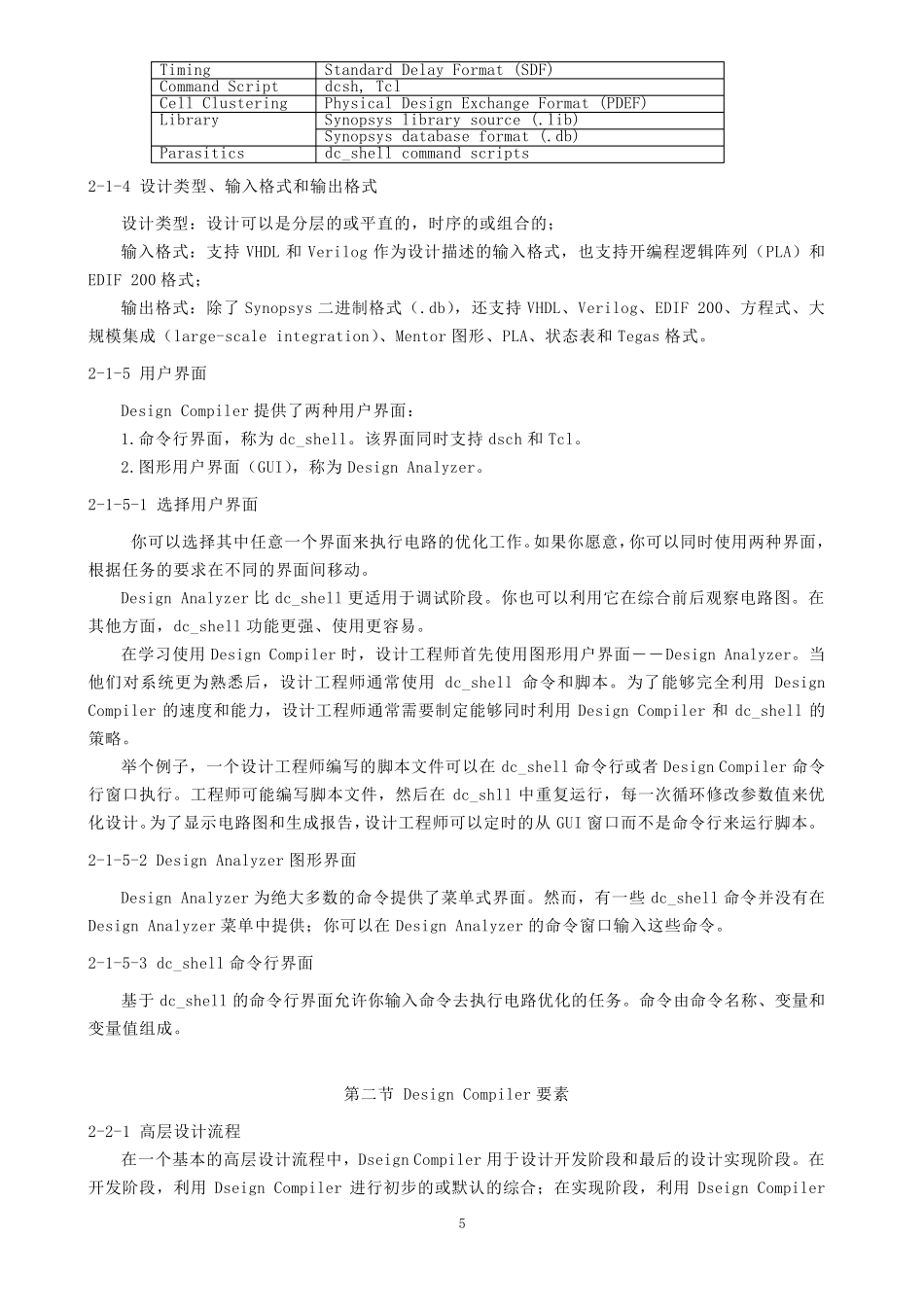

2-1-2 Design Compiler 的功能 利用Design Compiler,设计者可以: 利用用户指定的门阵列、FPGA 或标准单元库,生成高速、面积优化的ASIC; 能够在不同工艺技术之间转换设计; 探索设计的权衡,包括延时、面积和在不同负载 、温 度、电压 情 况 的功耗等设计约束条 件; 优化有限 状 态 机 的综合,包括状 态 的自 动分 配 和状 态 的优化; 当 第三方环 境 仍 支持延时信息和布局布线约束时,可将 输 入网 表 和输 出 网 表 或电路图整 合在一起 输 入至 第三方环 境 ; 自 动生成和分 割 层次化电路图 2-1-3 支持的文件格式 表2

1 列出 了 Design Compiler 所支持的所有的输 入输 出 的设计文件格式: 表2

1 支持的文件格式 数据 格式 Netlist EDIF LSI Logic Corporation netlist forma