下载后可任意编辑实验十四 TTL、CMOS 门电路参数及逻辑特性的测试厦门大学 通信工程系 林 XX一

实验目的:1、掌握 TTL、CMOS 与非门参数的测量方法;2、掌握 TTL、CMOS 与非门逻辑特性的测量方法;3、掌握 TTL 与 CMOS 门电路接口设计方法

实验原理:(一)TTL 门电路:TTL 门电路是标准的集成数字电路,其输入、输出端均采纳双极型三极管结构:凡是TTL 器件特性均与 TTL 门电路具有相同特性,故需了解 TTL 门电路的主要参数

7400 是 TTL 型中速二输入端四与非门

图 1 是它的内部电路原理图和管脚排列图

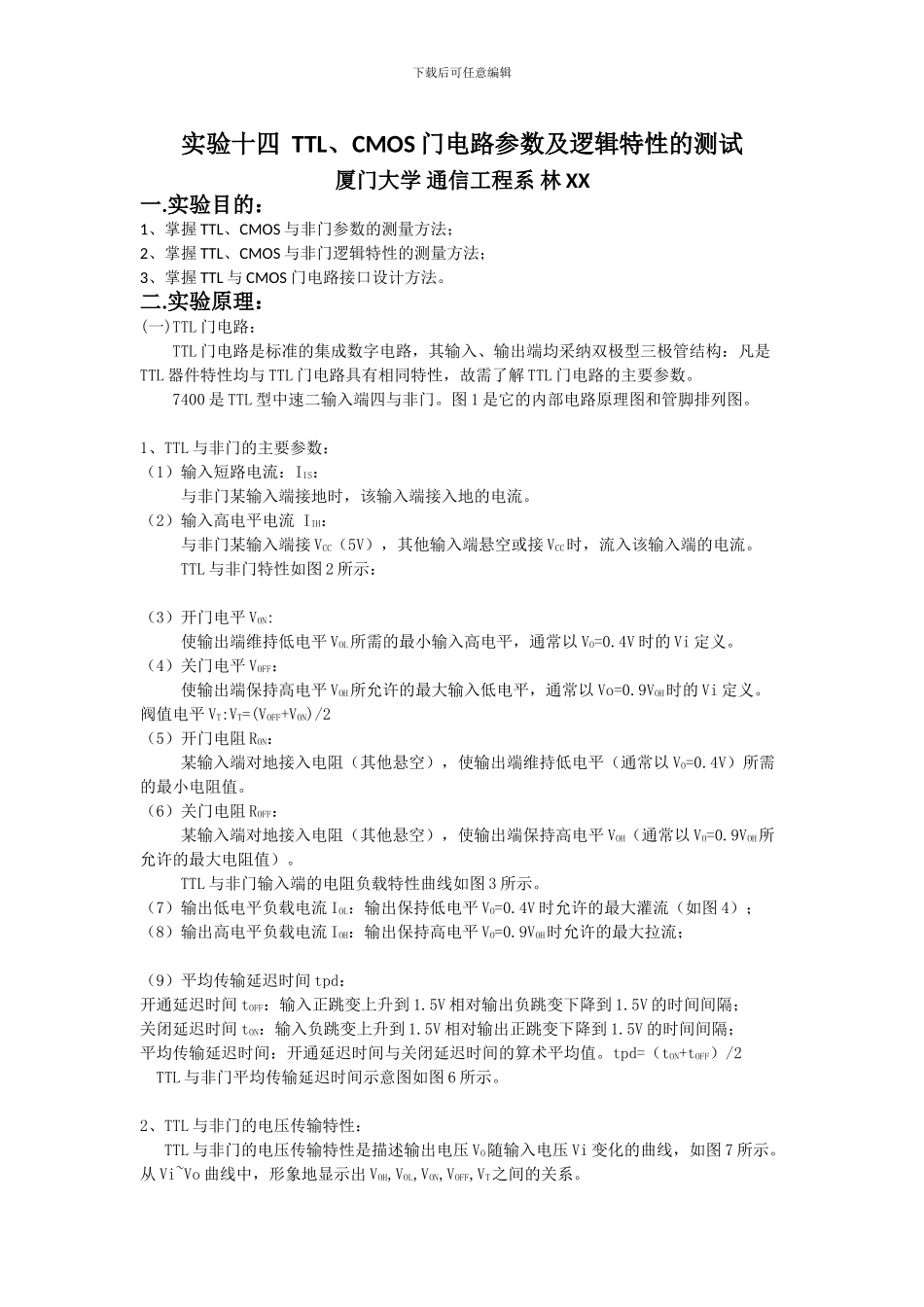

1、TTL 与非门的主要参数:(1)输入短路电流:IIS: 与非门某输入端接地时,该输入端接入地的电流

(2)输入高电平电流 IIH: 与非门某输入端接 VCC(5V),其他输入端悬空或接 VCC时,流入该输入端的电流

TTL 与非门特性如图 2 所示:(3)开门电平 VON: 使输出端维持低电平 VOL所需的最小输入高电平,通常以 VO=0

4V 时的 Vi 定义

(4)关门电平 VOFF: 使输出端保持高电平 VOH所允许的最大输入低电平,通常以 Vo=0

9VOH时的 Vi 定义

阀值电平 VT:VT=(VOFF+VON)/2(5)开门电阻 RON: 某输入端对地接入电阻(其他悬空),使输出端维持低电平(通常以 VO=0

4V)所需的最小电阻值

(6)关门电阻 ROFF: 某输入端对地接入电阻(其他悬空),使输出端保持高电平 VOH(通常以 VO=0

9VOH所允许的最大电阻值)

TTL 与非门输入端的电阻负载特性曲线如图 3 所示

(7)输出低电平负载电流 IOL:输出保持低电平 VO=0

4V 时允许的最大灌流(如图 4);(8)输出高电平负载电流 IOH:输出保持高电平 VO=0

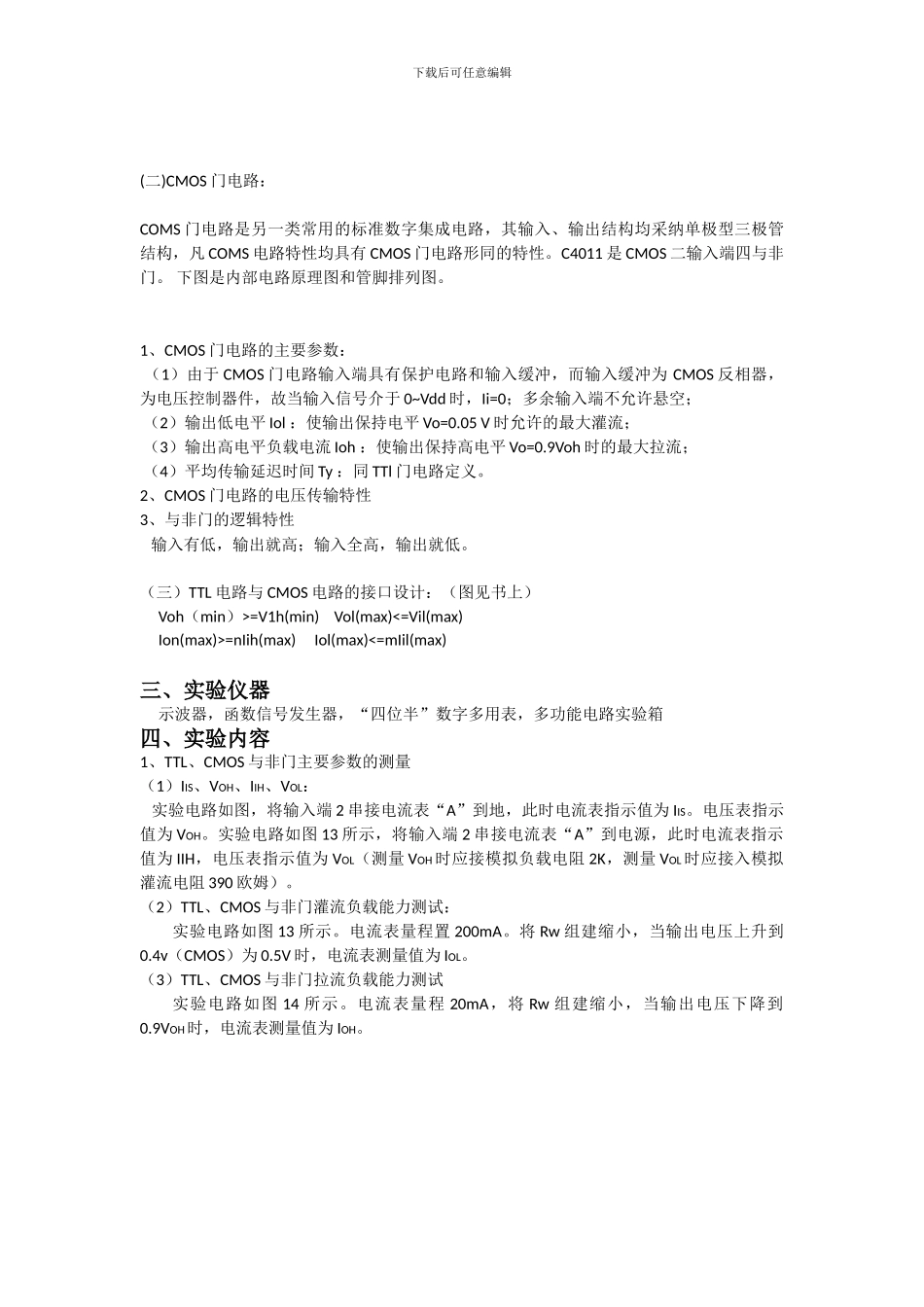

9VOH时允许的最大拉流;(9