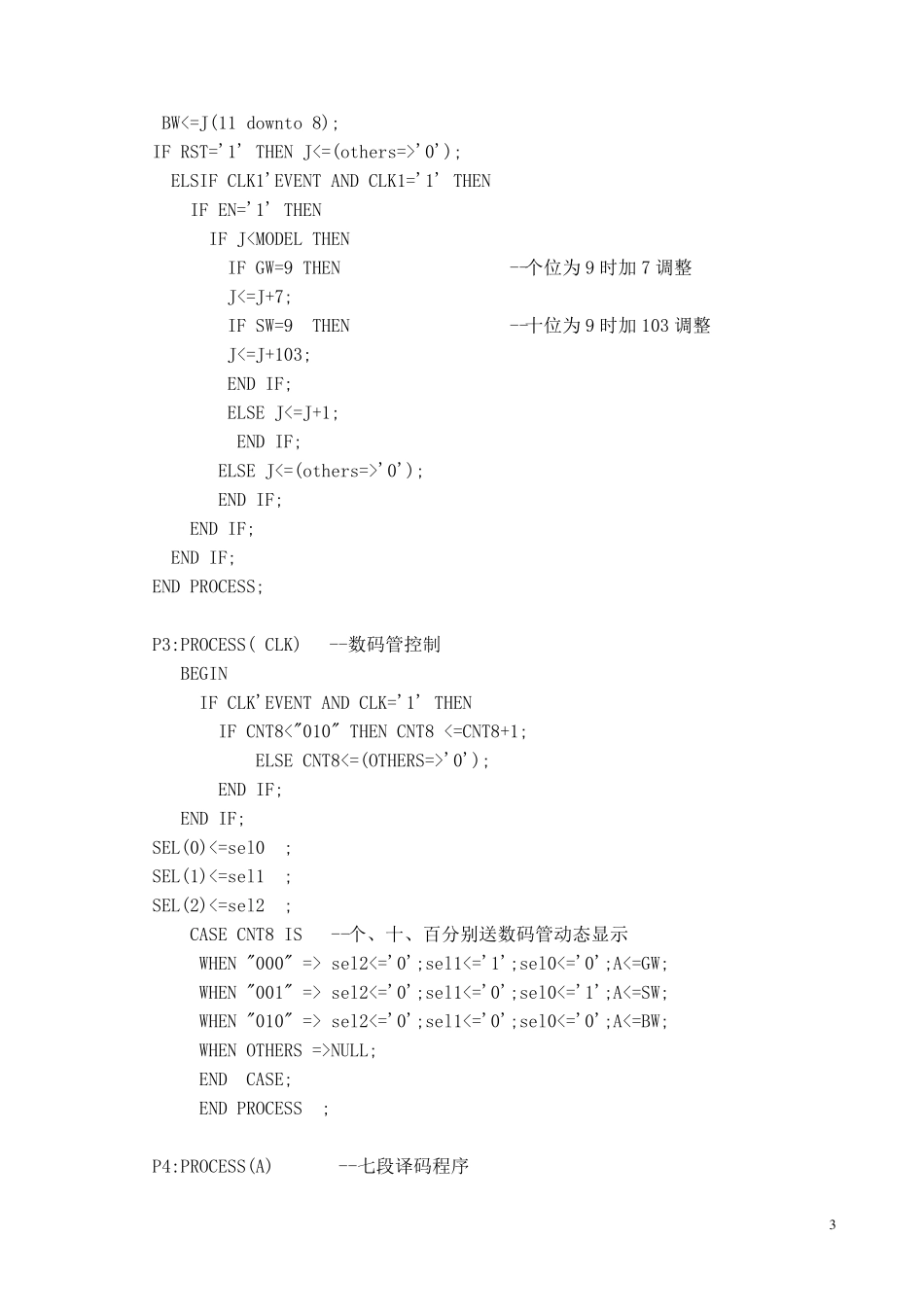

1 南昌大学实验报告 学生姓名: 邱永洪 学 号: 6 1 0 0 2 1 0 0 2 6 专业班级: 中兴1 0 1 班 实验类型: □ 验证 □ 综合 ■ 设计 □ 创新 实验日期: 2012.10. 19 实验二 模可变计数器的设计 一、实验目的 1、学习设计脉冲分频程序的设计,掌握分频的作用。 2、学会利用控制位 M 来控制计数器的模值。 二、实验内容与要求 1、计设置一位控制模的位 M,要求 M=0,模 23 计数;当 M=1,模 109 计数; 2、计数结果用三位数码管显示,显示 BCD 码; 3、利用 Qu artu s 软件实现波形仿真; 4、应用实验箱验证此计数器的功能。 三、实验思路 1、要求分别实现模 23 和模 109 的计数,因些我分别用 GW、SW、 BW 代表个位,十位和百位。还有一个控制模的位 M,当 M 为 0 时实现模 23 计数,只用到 GW 和 SW 分别为个位和十位;当 M 为 1 时实现模 109 计数,用 GW、SW、 BW 分别为个位,十位和百位计数。 2、由于要求用三个数码管显示,由于每次只能只能选中一个数码管显示管,因此我使用了数码管的动态扫描来实现视觉上多个数码管显示管同时显示的效果,这个步骤中分频计的作用很重要。我使用了一个可变的 R 作为分频计的初值。 3、计数时分两种情况 1)、当 M 为 0 时,实现模 23 计数,当个位为 9 则向十位进位,并个位清 0,当个位小于 9,则个位自身加 1;计数到 22 时当下一个时钟上升沿到来时就清 0 重计。 2)、当 M 为 1 时,实现模 109 计数,当个位为 9 则向十位进位,并个位清 0,当个位小于 9,则个位自身加 1;当个位和十位均为 9 时,就向百位进位,同时个位和十位自身清 0;计数到 108 时当下一个时钟上升沿到来时就清 0 重计。 四、实验程序 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY count IS 2 PORT(CLK,M,EN,RST:IN STD_LOGIC; R:IN STD_LOGIC_VECTOR(7 DOWNTO 0); ---分频计数初值 sel0,sel1,sel2:buffer STD_LOGIC; SG:OUT STD_LOGIC_VECTOR(7 DOWNTO 0); --数码管八段 CLK1:buffer STD_LOGIC; GW,SW,BW: buffer STD_LOGIC_VECTOR(3 DOWNTO 0);--计数器的个,十,百位 COUT:OUT STD_LOGIC;--溢出信号 SEL:OUT STD_LOGIC_VECTOR(7 DOWNTO 0) --位选信号 ); END count; ARCHITECTURE behav OF count IS ...