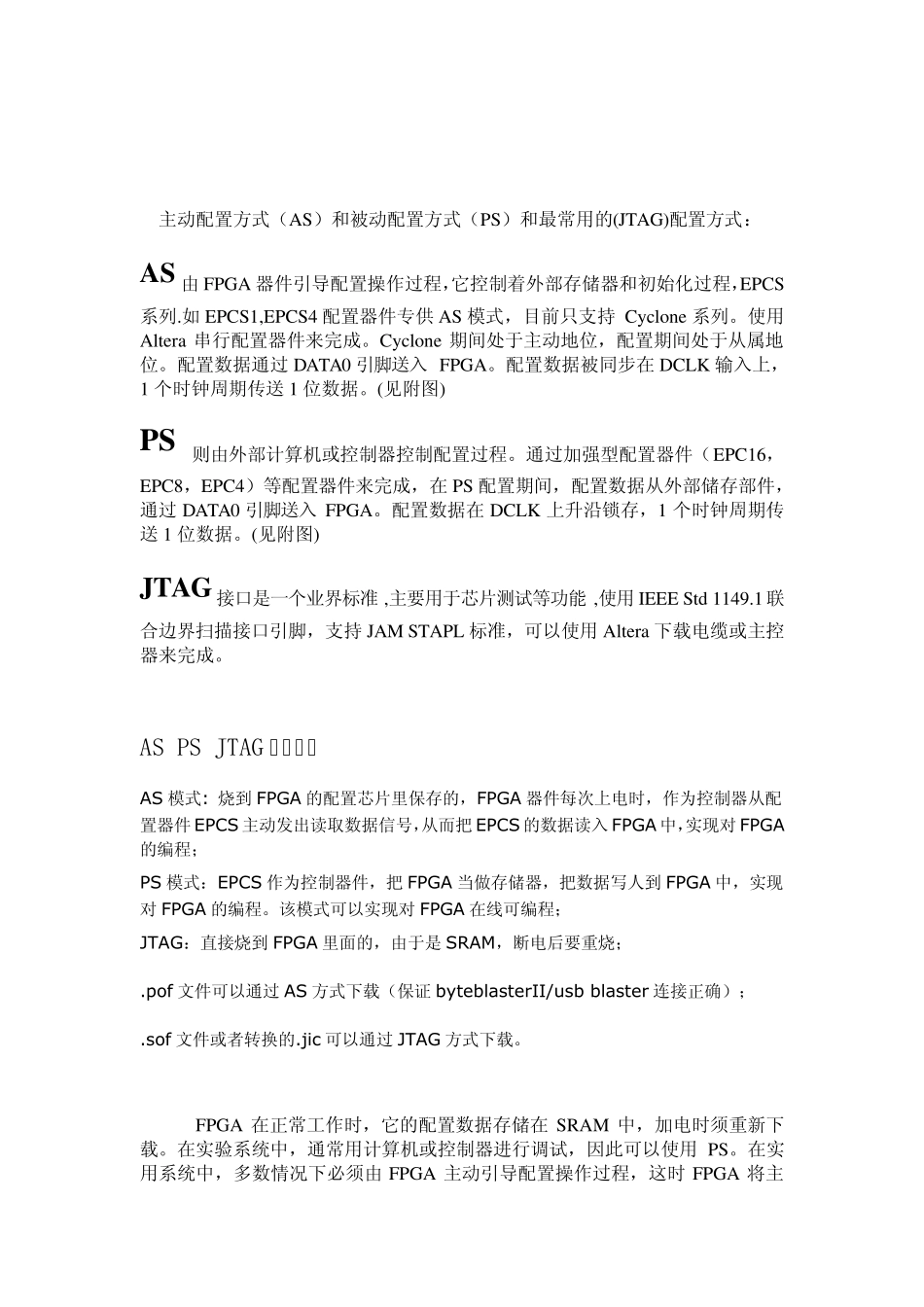

主动配置方式(AS)和被动配置方式(PS)和最常用的(JTAG)配置方式: AS 由FPGA 器件引导配置操作过程,它控制着外部存储器和初始化过程,EPCS系列

如EPCS1,EPCS4 配置器件专供AS 模式,目前只支持 Cy clone 系列

使用Altera 串行配置器件来完成

Cy clone 期间处于主动地位,配置期间处于从属地位

配置数据通过DATA0 引脚送入 FPGA

配置数据被同步在 DCLK 输入上,1 个时钟周期传送 1 位数据

(见附图) PS则由外部计算机或控制器控制配置过程

通过加强型配置器件(EPC16,EPC8,EPC4)等配置器件来完成,在 PS 配置期间,配置数据从外部储存部件,通过DATA0 引脚送入 FPGA

配置数据在 DCLK 上升沿锁存,1 个时钟周期传送 1 位数据

(见附图) JTAG 接口是一个业界标准 ,主要用于芯片测试等功能 ,使用IEEE Std 1149

1 联合边界扫描接口引脚,支持JAM STAPL 标准,可以使用Altera 下载电缆或主控器来完成

AS PS JTAG 的区别: AS 模式: 烧到 FPGA 的配置芯片里保存的,FPGA 器件每次上电时,作为控制器从配置器件EPCS 主动发出读取数据信号,从而把 EPCS 的数据读入 FPGA 中,实现对 FPGA的编程; PS 模式:EPCS 作为控制器件,把 FPGA 当做存储器,把数据写人到 FPGA 中,实现对 FPGA 的编程

该模式可以实现对 FPGA 在线可编程; JTAG:直接烧到 FPGA 里面的,由于是 SRAM,断电后要重烧;

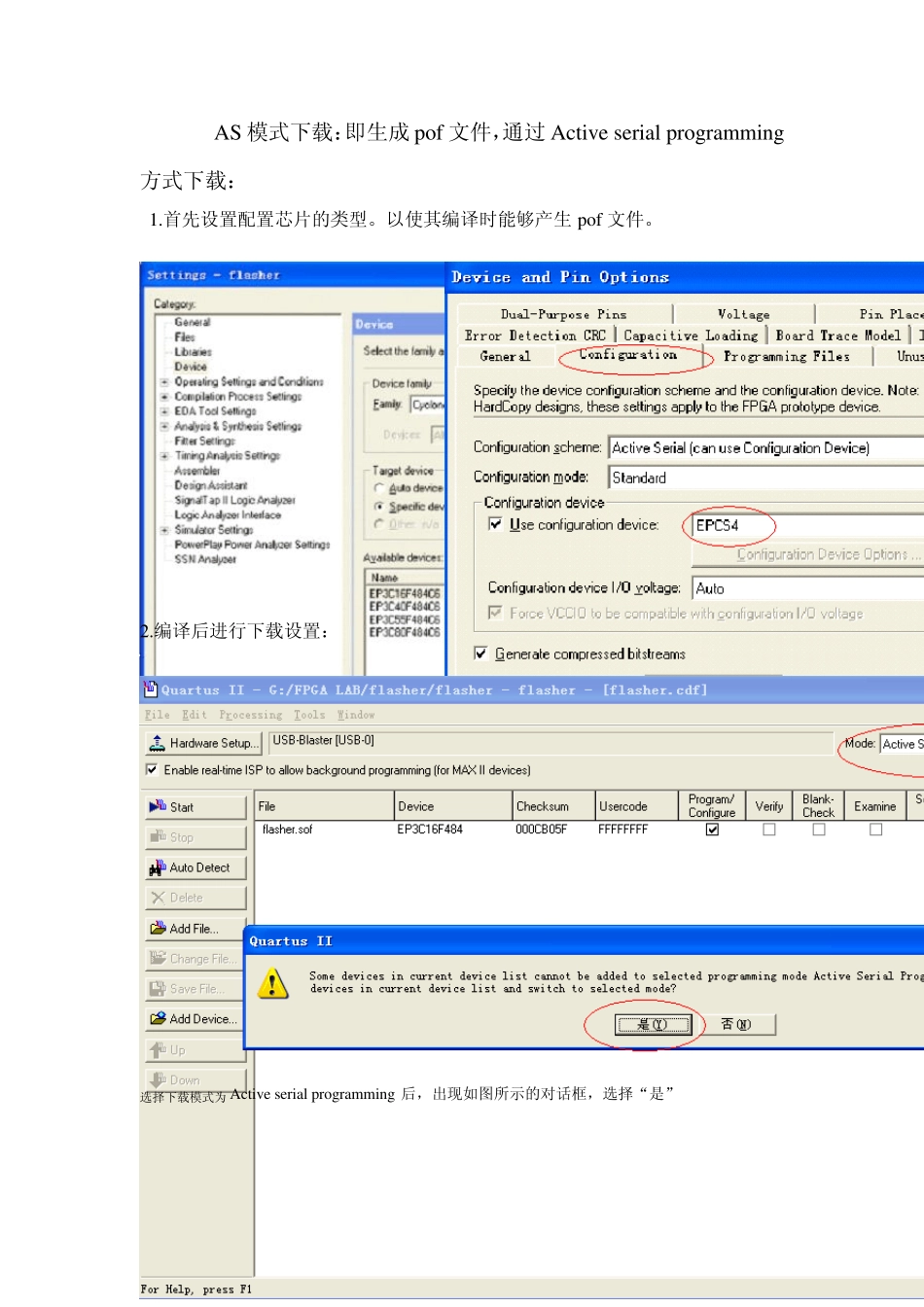

pof 文件可以通过AS 方式下载(保证 byteblasterII/usb blaster 连接正确);

sof 文件或者转换的

jic 可以通过JTAG 方式下载

FPGA 在正常工作时,它的配置数据