数字钟设计 一、实验目的: 用 verilog HDL 语言在 EP1C12Q240C8 的 FPGA 开发平台上实现多能数字钟;要求实现时间显示、时间设置、闹钟功能、秒表功能等 二、实验内容 1) 计时,时间以 24h制显示,第二位数码管的小数点闪烁表征秒表; 2) 校时,分四位数码管进行校时,可以实现校时的改变,用数码管小数点表示所较位所在; 3) 闹钟:设定闹钟时间,用蜂鸣器提示,并且可以实现闹钟的停止; 4) 跑表:启动、暂停、清零; 三、实验器件(FPGA 开发板上) 1) 输入:4个按键 K1、K2、 K3、K4 2) 输出:4个数码管,2个 LED,1个蜂鸣器 3) 4位数码管显示时钟的时和分或跑表的计时 4) 蜂鸣器可作为闹钟提示的提示音乐 设计思路 1) 按键功能:K1 完成四个功能的切换显示并通过 led1 与 led2 显示功能选择;时间设置中用 K2 设置小时 K3 设置分钟;闹钟功能中时间设置同时间设置,K4 关闭闹钟;跑表功能中 K2 开始、K3 暂停,K4 清零

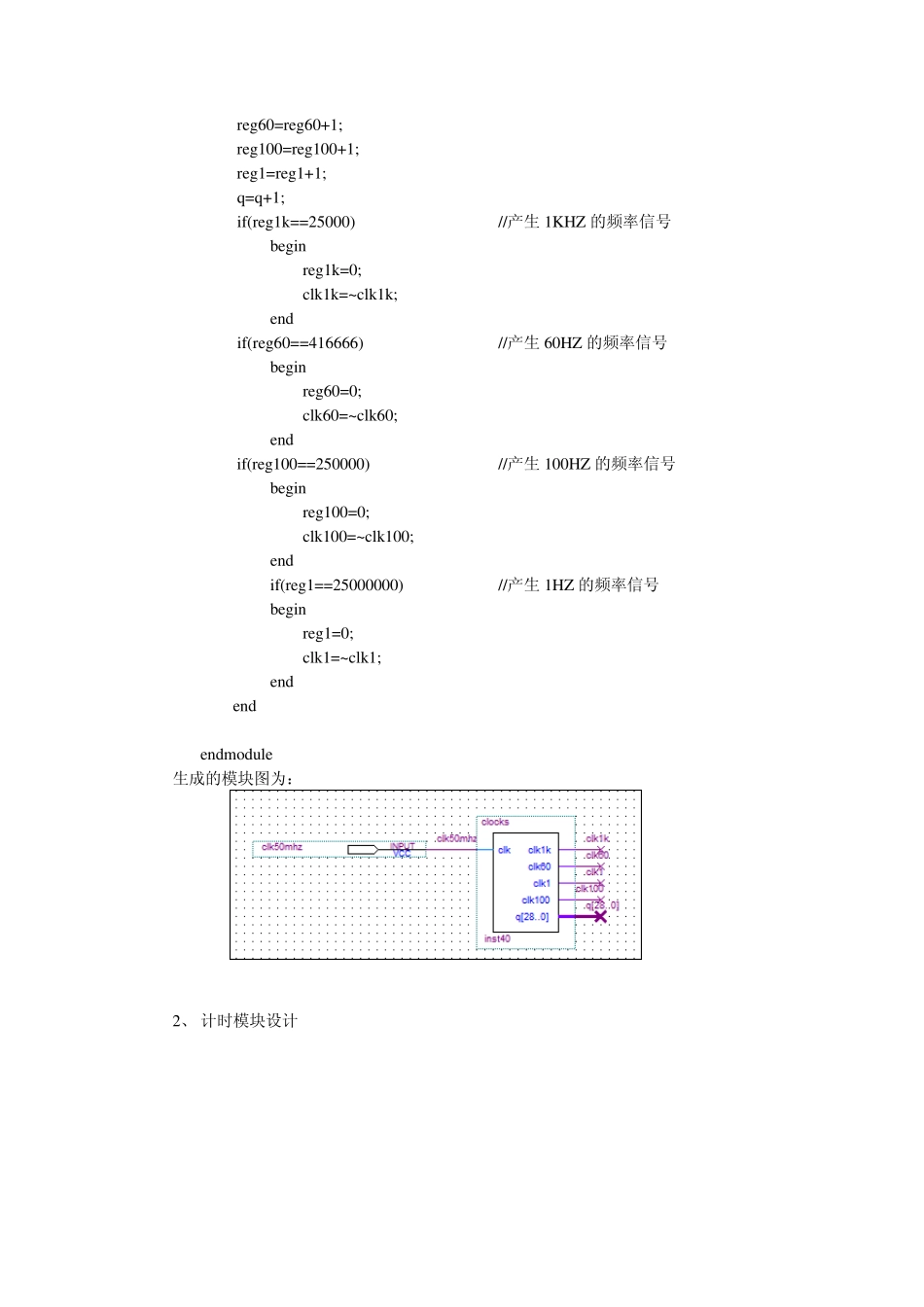

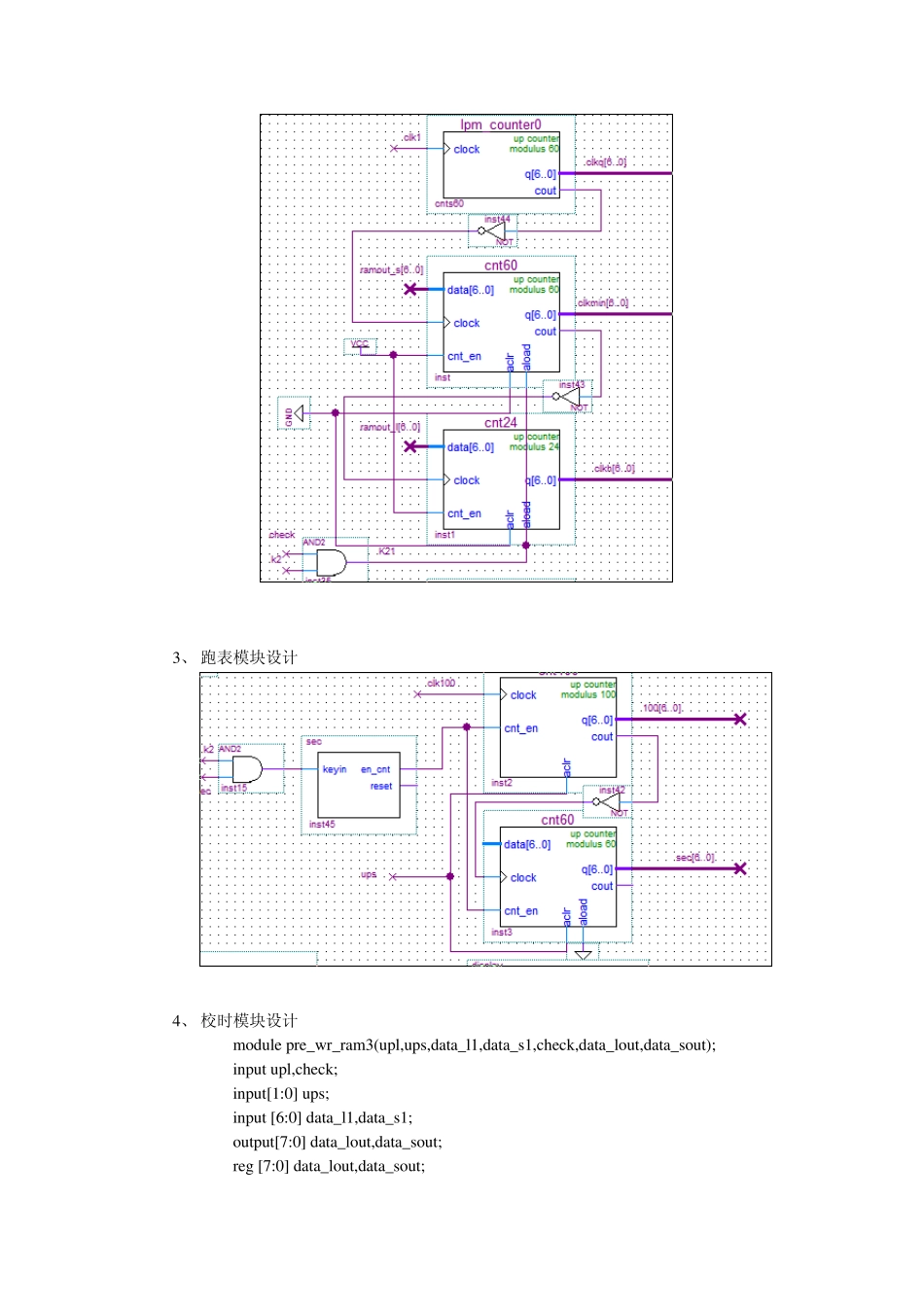

2) 模块设计:计时、校时、跑表和闹钟

3) 显示设计:在功能切换时数码管的显示也发生变化,计时功能中,显示小时、分钟并且通过第三位数码管的小数点的闪烁表示秒表的计时;校时和闹钟功能中,显示小时、分钟并且通过显示数码管的小数点表征当前数码管的数据处于校时状态;跑表数码管显示的最高位为秒,且无小数点点亮

同时用两个 LED 的点亮情况来表征当前所在的功能状态,计时LED1、LED2 均亮,校时 LED1 灭、LED2 亮,闹钟LED1 亮、LED2 灭,跑表 LED1、LED2均灭

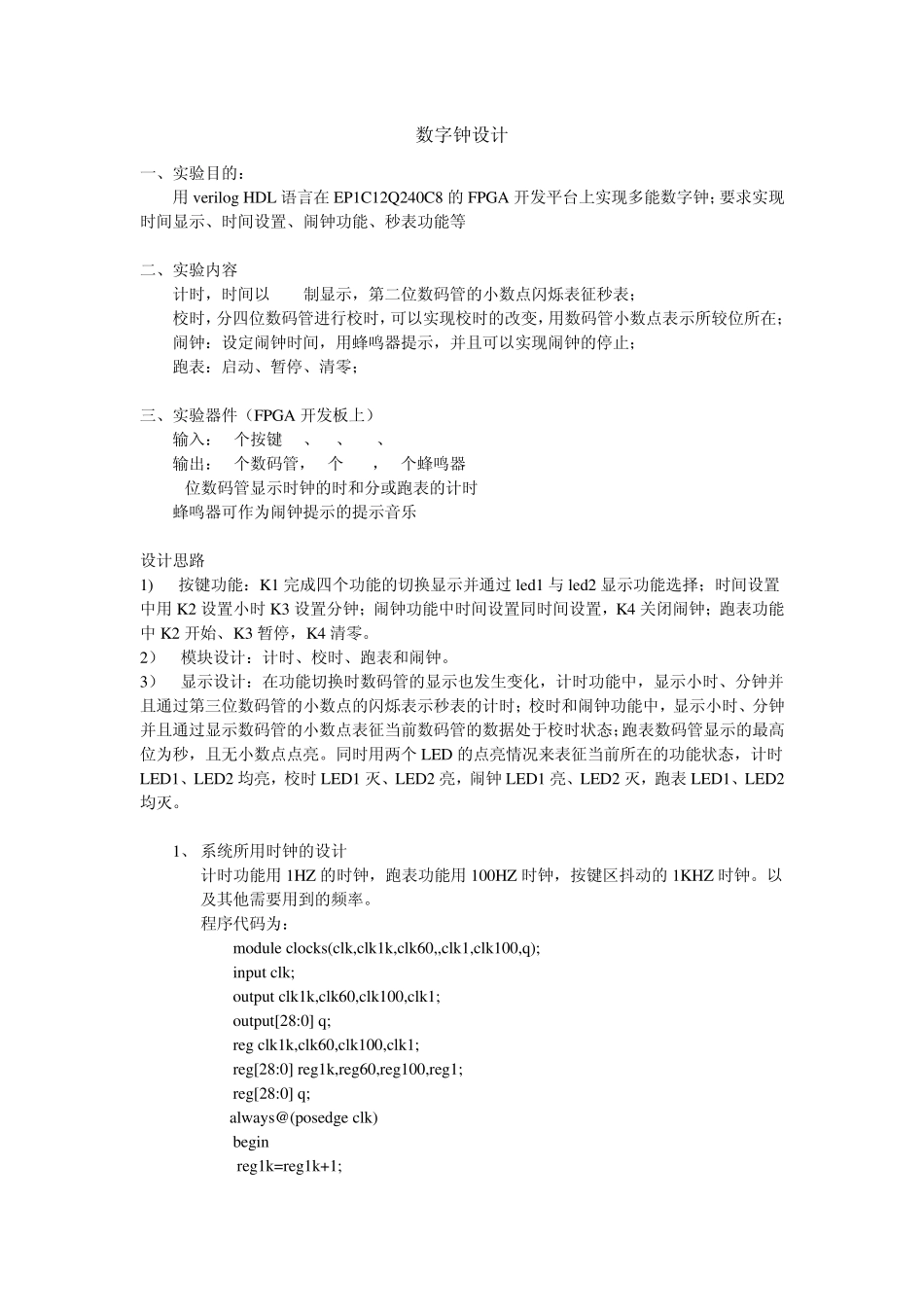

1、 系统所用时钟的设计 计时功能用 1HZ 的时钟,跑表功能用 100HZ 时钟,按键区抖动的 1KHZ 时钟

以及其他需要用到的频率

程序代码为: module clocks(clk,clk1k,