Integrated Silicon Solution, Inc

— 1-800-379-47741TARGET SPECIFICATIONRev

C05/04/01IS42S16400ISSI®This document contains TARGET SPECIFICATION data

ISSI reserves the right to make changes to its products at any time without notice in order to improve design and supply the bestpossible product

We assume no responsibility for any errors which may appear in this publication

© Copyright 2001, Integrated Silicon Solution, Inc

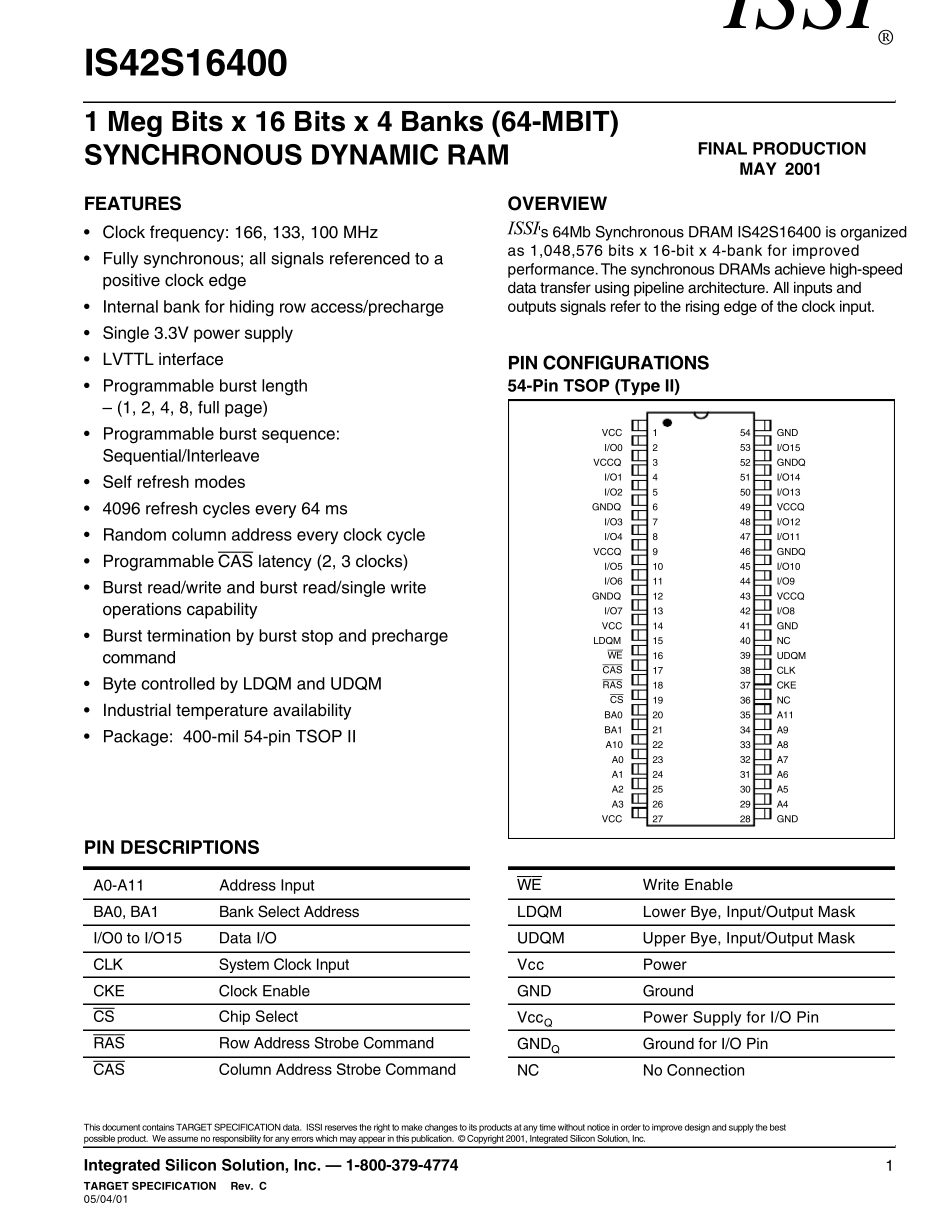

FEATURES• Clock frequency: 166, 133, 100 MHz• Fully synchronous; all signals referenced to apositive clock edge• Internal bank for hiding row access/precharge• Single 3

3V power supply• LVTTL interface• Programmable burst length– (1, 2, 4, 8, full page)• Programmable burst sequence:Sequential/Interleave• Self refresh modes• 4096 refresh cycles every 64 ms• Random colum