IS61LV25616AL 3

3V 的256K x 16 高速静态随机存储器

特点: 高速存取时间:10,12ns CMOS 低功耗工作 低备用电源,低于 5mA 的备用电源 TTL 兼容接口电平 3

3V 电源单独供电 全静态操作:无需刷新,无需时钟 三态输出 数据控制为上部或下部字节 可在工业温度下使用 说明: IS61LV25616AL 是由高速的,4,194,304 字节静态RAM,由 16 位的262,144 字节组成

并利用 ISSI 的高性能 CMOS 技术合成

这种高可靠性的处理加上创新的电路设计技术,生产出高性能,低功耗的设备

当/CE 是高电平(悬空)时,设备呈现待机模式,并且此时的功耗可以降低到 CMOS输入时的功耗

简单的存储器扩展是由芯片使能端和输出使能端来提供,/CE 和/OE

激活低电平的/WE可以同时控制存储器的读和写

数据字节既允许高字节(/UB)进入,也允许低字节(/LB)进入

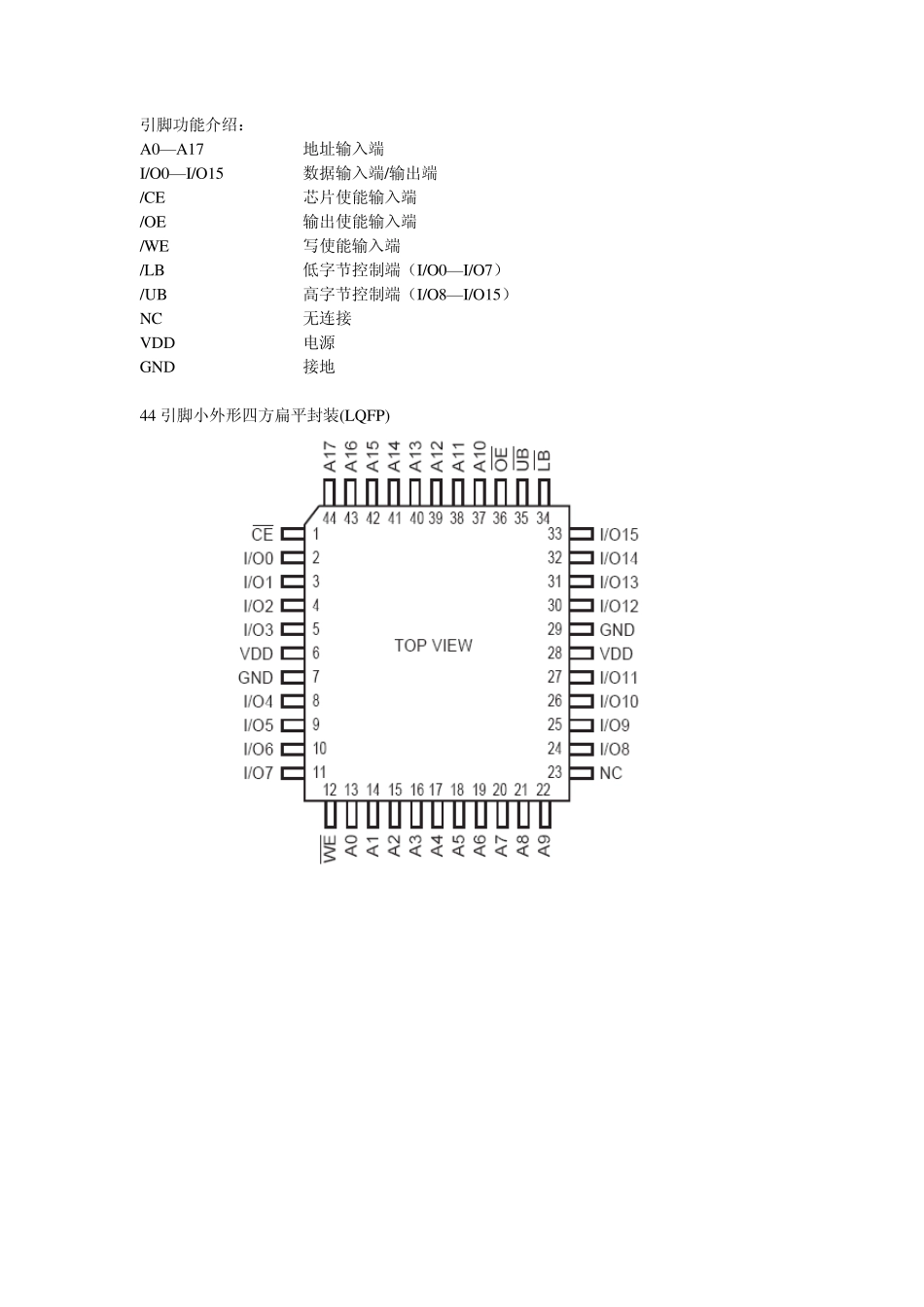

IS61LV25616AL 被按照 JEDEC(联合电子设备工程会议)分别打包成 44 引脚 400mil(千分之一寸)J 型塑料封装(SOJ),44 引脚微型薄片 II 式封装(TSOP),44 引脚小外形四方扁平封装(LQFP)和 48 引脚迷你球状栅级阵列型封装(BGA)(8mm x 10mm)

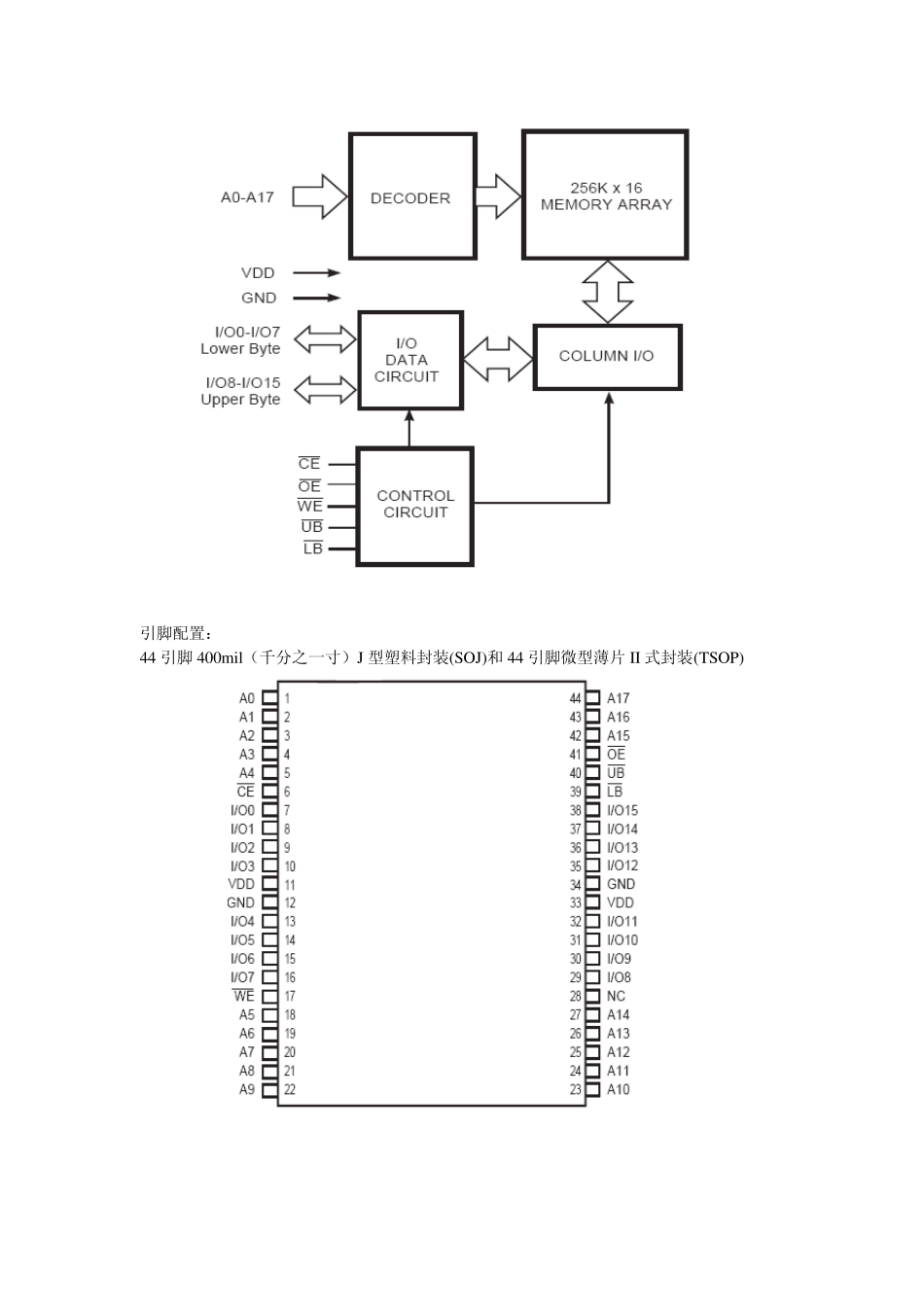

原理框图如下: 引脚配置: 44 引脚400m il(千分之一寸)J 型塑料封装(SOJ)和 44 引脚微型薄片 II 式封装(TSOP) 引脚功能介绍: A0—A17 地址输入端 I/O0—I/O15 数据输入端/输出端 /CE 芯片使能输入端 /OE 输出使能输入端 /W E 写使能输入端 /LB 低字节控制端(I/O0—I/O7) /UB 高字节控制端(I/O8—I/O15) NC 无连接 VDD 电源 GND