- 1 - 第一章 ispPAC简介 1999年11月,Lattice公司推出了在系统可编程模拟电路(In-System -Programmability Programmable Analog Circuits,以下简称ispPAC),为电子设计自动化(EDA)技术的应用开拓了广阔的前景

与数字在系统可编程大规模集成电路(ispLSI)一样,ispPAC允许设计者使用开发软件通过计算机对模拟电路进行设计、修改、仿真,最后通过编程电缆将设计方案下载至芯片中

ispPAC可实现以下三种功能: (1) 信号调理:对信号进行放大、衰减、滤波

(2) 信号处理:对信号进行求和、求差、积分运算

(3) 信号转换:把数字信号转换成模拟信号

目前已推出了五种芯片:ispPAC10,ispPAC20,ispPAC30,ispPAC80和 ispPAC81

ispPAC的开发软件为PACDesigner,软件主要特征: (1) 设计输入方式:原理图输入; (2) 模拟仿真:测试电路的幅频和相频特性; (3) 支持器件:ispPAC10、ispPAC20、ispPAC30、ispPAC80、ispPAC81; (4) 内含用于低通滤波器设计的宏; (5) 能将设计直接下载; 一、ispPAC20的结构 在系统可编程模拟电路提供三种可编程性能: (1) 可编程功能:具有对模拟信号进行放大、转换、滤波的功能

(2) 可编程互联:能把器件中的多个功能块进行互联,能对电路进行重构,具有百分之百的 电路布通率

(3) 可编程特性:能调整电路的增益、带宽和阈值

ispPAC器件可反复编程,编程次数可达 1万次以上

高集成度、高精确度的设计集于一片ispPAC器件中,取代了由许多分立元件组成所实现的电路功能

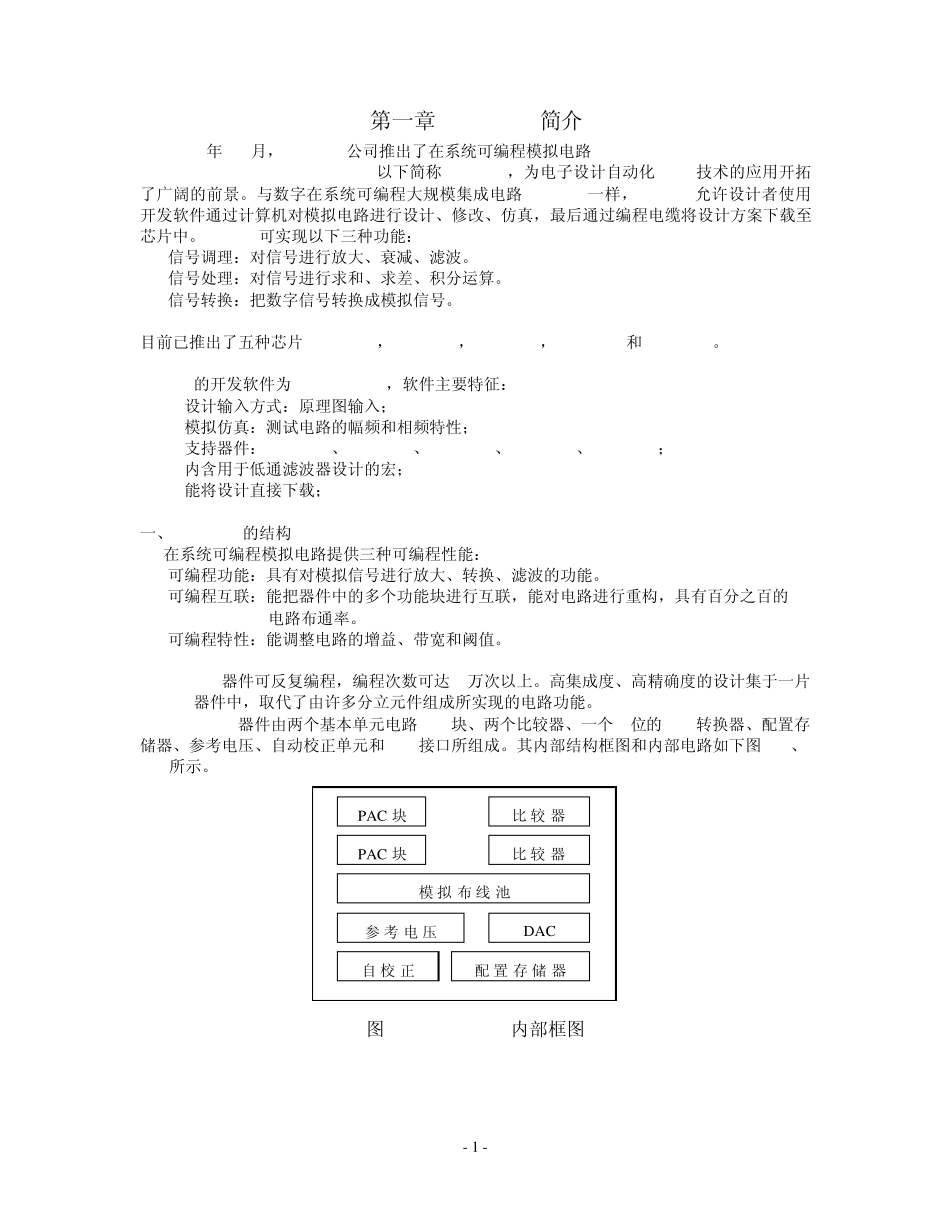

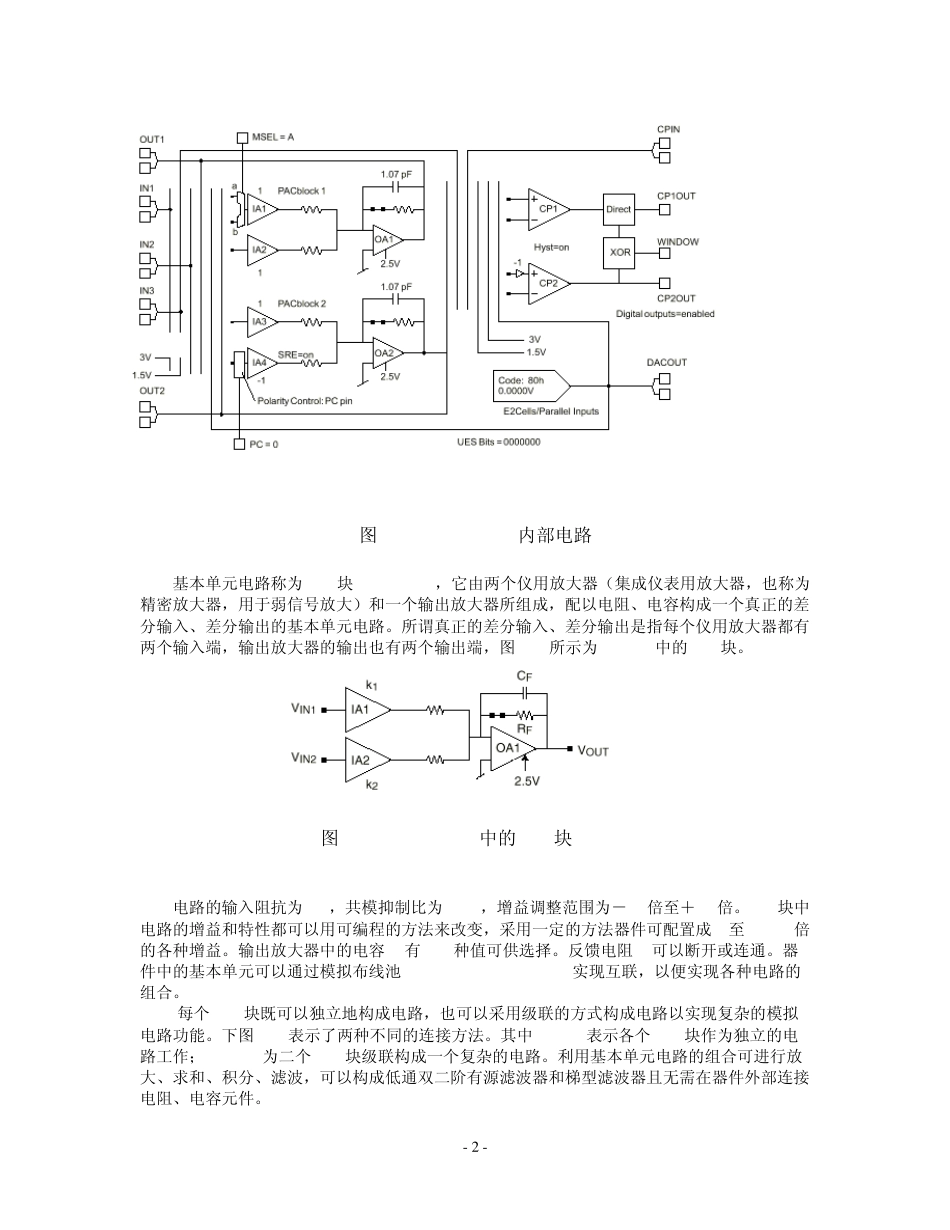

ispPAC20器件由两个基本单元电路PAC块、两个比较器、一个 8位的D/A转换器