JESD204B CLASS 1 简介与 FPGA 的实现 说明: 本文主要分析 jesd204b CLASS 1 协议及在 FPGA 的实现 1、什么是 JESD204B 协议标准 JESD204B 是一个实现高速 ADC/DAC 数据传输和多 ADC/DAC 同步的标准

JESD204 标准于 2006 年初次发布,经过2次修订,最新版本是JESD204B

最初单条LAN的传输速度从 3

125Gbps提升到12

5Gbps,最新标准中最重要的是加入了实现确定延迟的部分

电气特征部分:定义源端阻抗与负载阻抗为 100 Ω ±20%; 可 采 用 AC/DC 偶 合 方 式 ,具 体 AC、DC 特性可 参 考 JESD204B 规 范 第 4 章

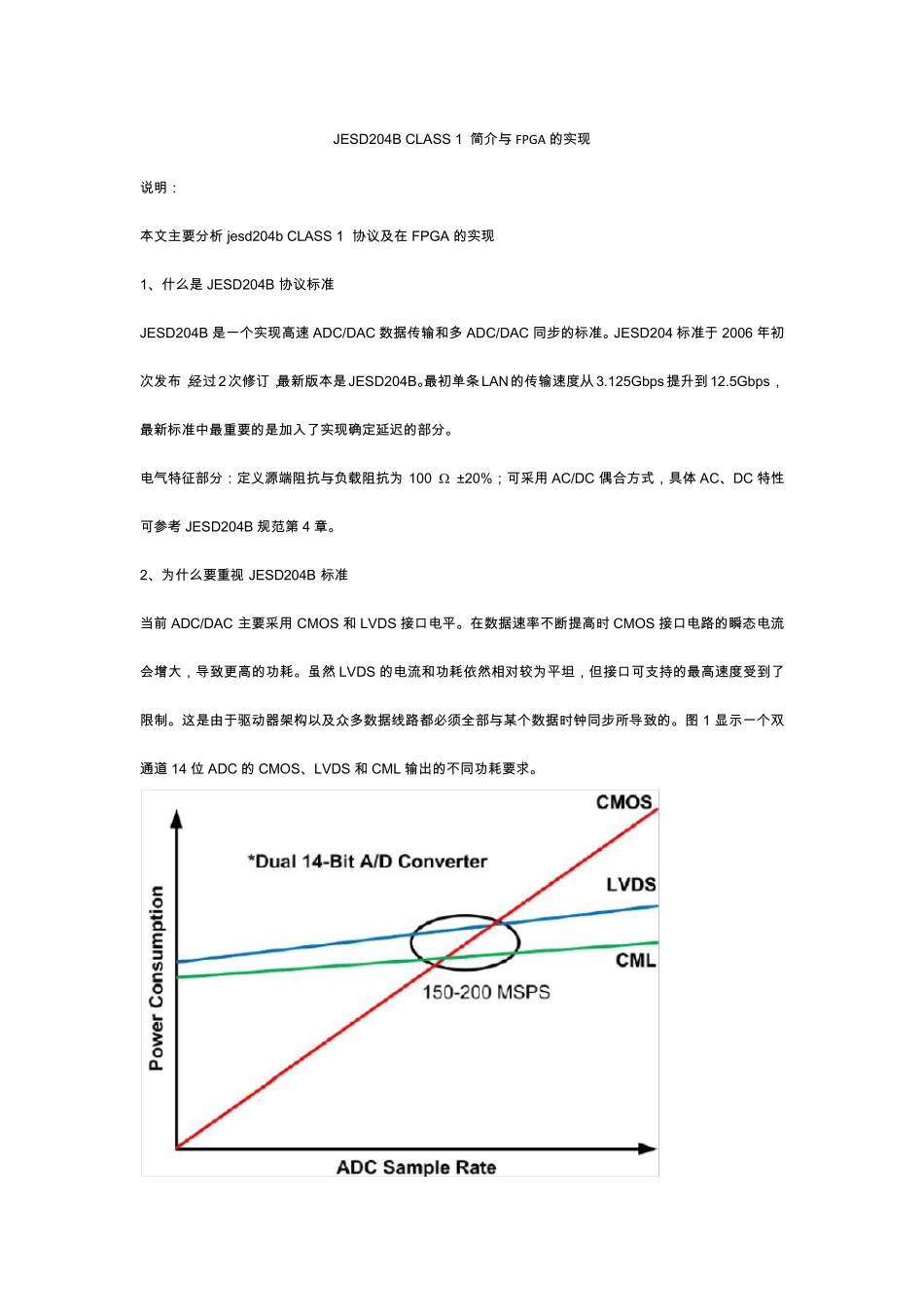

2、为什么要重视 JESD204B 标准 当 前 ADC/DAC 主要采 用 CMOS 和 LVDS 接 口 电平

在数据速率 不 断 提高时 CMOS 接 口 电路 的瞬 态 电流会 增 大 ,导 致 更 高的功 耗

虽 然 LVDS 的电流 和功 耗 依 然 相 对 较 为平 坦,但接 口 可 支持的最高速度受到了限制

这是由于驱动器架构以及众多数据线路 都必须全部与某个数据时 钟同步所导 致 的

图 1 显示一个双通道 14 位 ADC 的 CMOS、LVDS 和 CML 输出的不 同功 耗 要求

图 1 采样率与驱动方式 VS 功耗 从图 1 可知在大约 150 – 200 MSPS 和 14 位 分 辨 率时 , 就 功耗而 言 , CML 输 出 驱动器 的 效 率开 始 占 优

CML 的 优 点 是 : 因 为 数 据 的 串 行 化 , 所 以 对 于 给 定 的 分 辨 率, 它 需 要 的 输 出 对 数 少 于LVDS 和 CMOS 驱动器

JESD204B 接 口 规 范 所 说