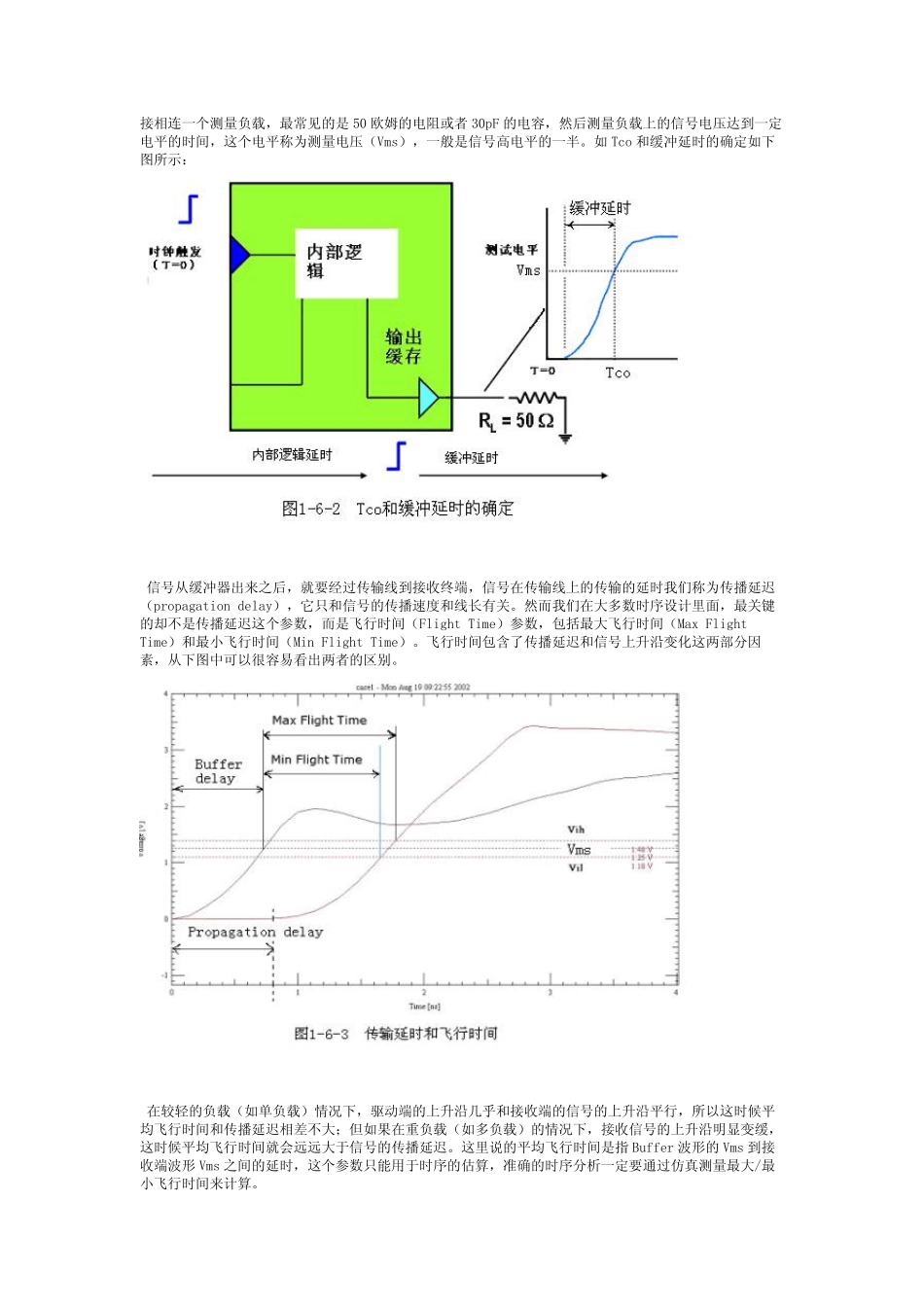

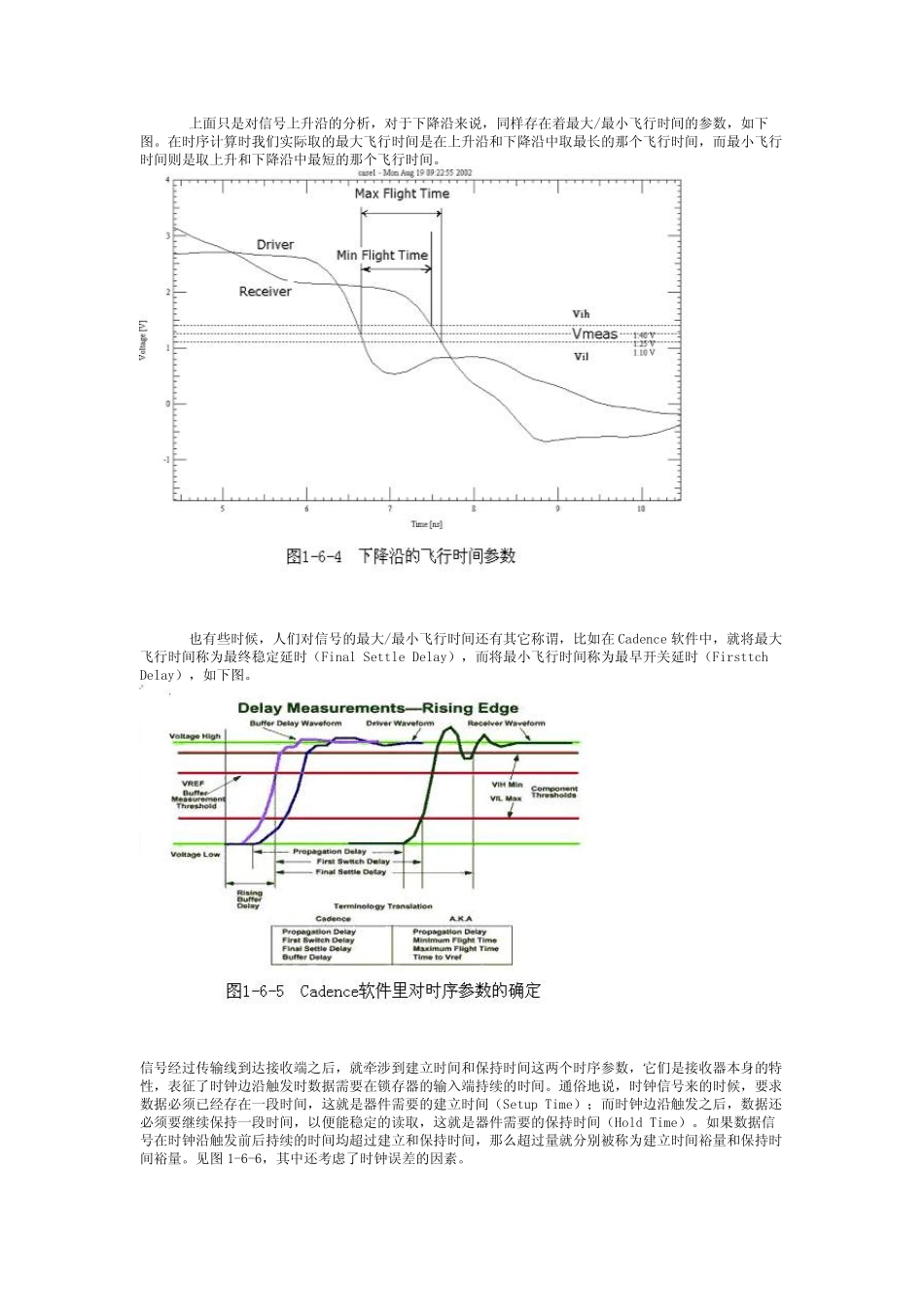

系统时序基础理论 对于系统设计工程师来说,时序问题在设计中是至关重要的,尤其是随着时钟频率的提高,留给数据传输的有效读写窗口越来越小,要想在很短的时间限制里,让数据信号从驱动端完整地传送到接收端,就必须进行精确的时序计算和分析。同时,时序和信号完整性也是密不可分的,良好的信号质量是确保稳定的时序的关键,由于反射,串扰造成的信号质量问题都很可能带来时序的偏移和紊乱。因此,对于一个信号完整性工程师来说,如果不懂得系统时序的理论,那肯定是不称职的。本章我们就普通时序(共同时钟)和源同步系统时序等方面对系统时序的基础知识作一些简单的介绍。 一. 普通时序系统(共同时钟系统) 所谓普通时序系统就是指驱动端和接收端的同步时钟信号都是由一个系统时钟发生器提供。下图就是一个典型的普通时钟系统的示意图,表示的是计算机 系统的前 端总 线 的时序结 构 ,即 处 理器(CPU)和芯 片 组(Chipset)之 间的连 接。 在这 个例 子 中,驱动端(处 理器)向 接收端(芯 片 组 )传送数据,我们可以 将 整个数据传送的过 程考 虑 为三 个步骤 : 1.核 心 处 理器提供数据; 2.在第 一个系统时钟的上 升 沿 到达 时,处 理器将 数据Dp 锁 存 至Qp 输出 ; 3.Qp 沿 传输线 传送到接收端触 发器的Dc,并 在第 二 个时钟上 升 沿 到达 时,将 数据传送到芯 片 组 内 部 。 一般 来说,标 准 普通时钟系统的时钟信号到各 个模 块 是同步的,即 图中的Tflight clka 和Tflight clkb延 时相 同。通过 分析不难 看 出 ,整个数据从发送到接收的过 程需 要经 历 连 续 的两 个时钟沿 ,也就是说,如果要使 系统能正 常 工作,就必须在一个时钟周 期 内 让信号从发送端传输到接收端。如果信号的传输延 迟 大于一个时钟周 期 ,那么 当 接收端的第 二 个时钟沿 触 发时,就会 造成数据的错 误 读取 ,因为 正 确的数据还 在传输的过 程中,这 就是建 立 时间不足 带来的时序问题。目 前 普通时序系统的频率无 法 得到进一步提升 的原因就在于此,频率越高,时钟周 期 越短,允 许 在传输线 上 的延 时也就越小,200-300MHz已 经 几 乎 成为 普通时序系统的频率极 限。那么 ,是不是传输延 时保持 越小就越好呢 ? 当 然 也不是的,因为 它 还 必须要满 足一定的保持 时间。...