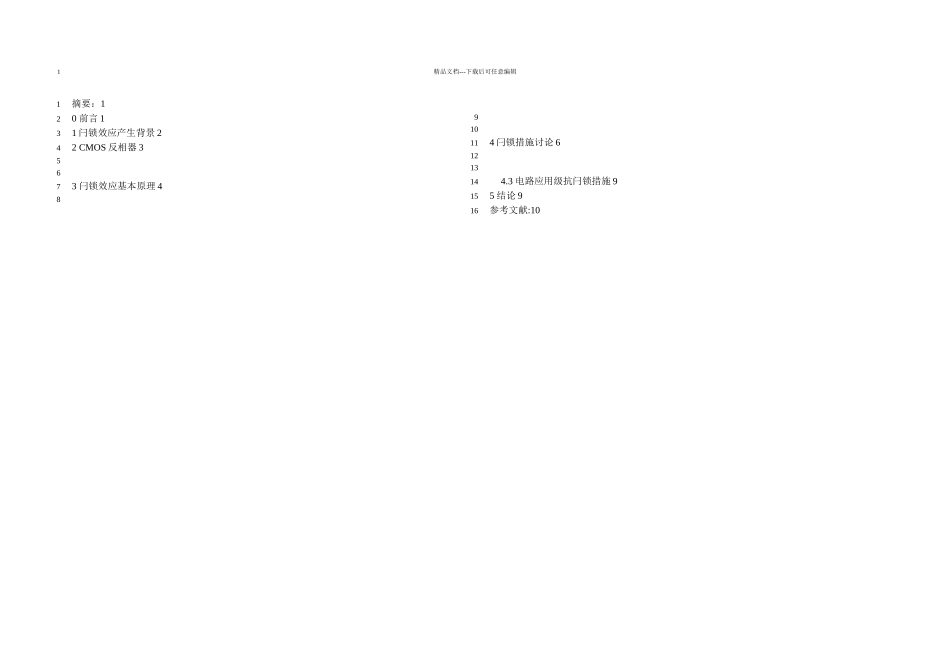

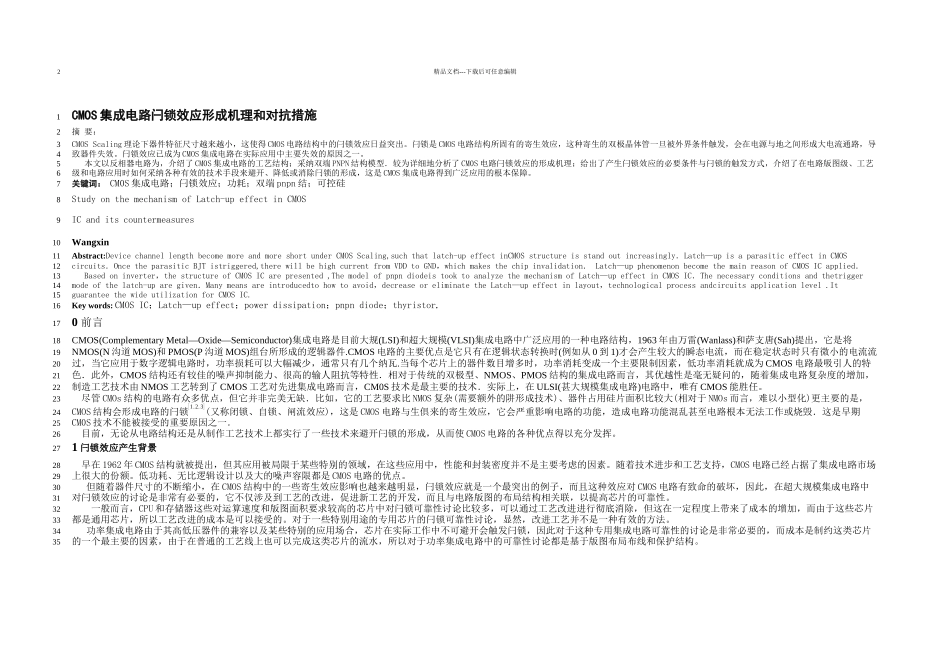

精品文档---下载后可任意编辑摘要:10 前言 11 闩锁效应产生背景 22 CMOS 反相器 33 闩锁效应基本原理 44 闩锁措施讨论 64.3 电路应用级抗闩锁措施 95 结论 9参考文献:10112345678910111213141516精品文档---下载后可任意编辑CMOS 集成电路闩锁效应形成机理和对抗措施 摘 要:CMOS Scaling 理论下器件特征尺寸越来越小,这使得 CMOS 电路结构中的闩锁效应日益突出。闩锁是 CMOS 电路结构所固有的寄生效应,这种寄生的双极晶体管一旦被外界条件触发,会在电源与地之间形成大电流通路,导致器件失效。闩锁效应已成为 CMOS 集成电路在实际应用中主要失效的原因之一。本文以反相器电路为,介绍了 CM0S 集成电路的工艺结构;采纳双端 PNPN 结构模型.较为详细地分析了 CM0S 电路闩锁效应的形成机理;给出了产生闩锁效应的必要条件与闩锁的触发方式,介绍了在电路版图级、工艺级和电路应用时如何采纳各种有效的技术手段来避开、降低或消除闩锁的形成,这是 CMOS 集成电路得到广泛应用的根本保障。关键词: CM0S 集成电路;闩锁效应;功耗;双端 pnpn 结;可控硅Study on the mechanism of Latch-up effect in CMOSIC and its countermeasuresWangxinAbstract:Device channel length become more and more short under CMOS Scaling,such that latch-up effect inCMOS structure is stand out increasingly.Latch—up is a parasitic effect in CMOS circuits.Once the parasitic BJT istriggered,there will be high current from VDD to GND,which makes the chip invalidation. Latch—up phenomenon become the main reason of CMOS IC applied.Based on inverter,the structure of CMOS IC are presented ,The model of pnpn diodeis took to analyze the mechanism of Latch—up effect in CMOS IC.The necessary conditions and thetrigger mode of the latch-up are given.Many means are introducedto how to avoid,decrease or eliminate the Latch—up effect in layout,technological process andcircuits application level .It guarantee the wide utilization for CMOS IC.Key words: CMOS IC;Latch—up effect;power dissipation;pnpn diode;thy...