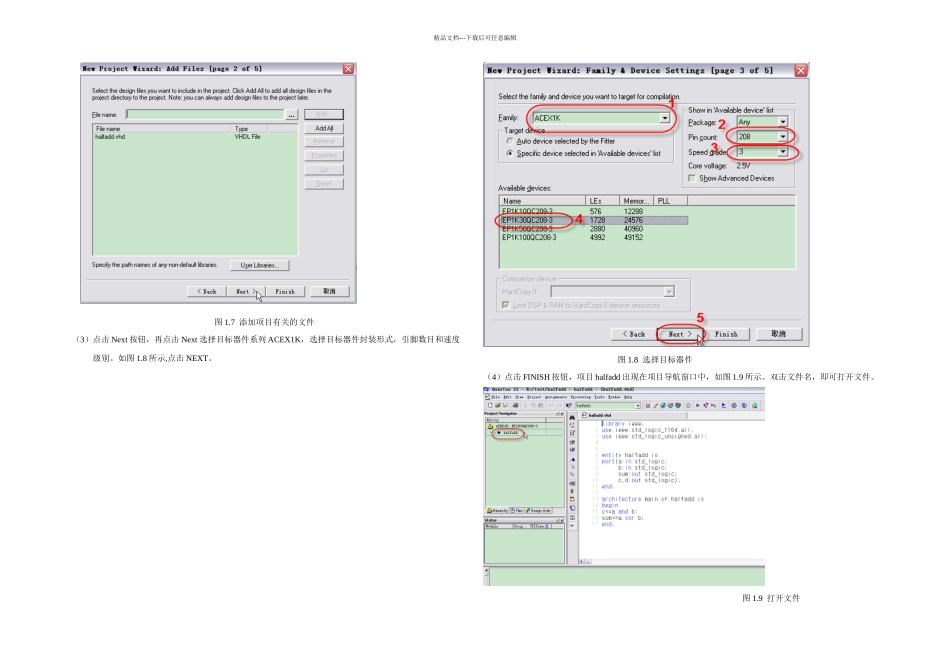

精品文档---下载后可任意编辑一、实验目的1. 熟悉 Quartus Ⅱ 软件基本使用方法;2.掌握电路的基本设计方法;3.掌握电路的基本仿真方法;4.掌握电路的基本下载方法。二、实验内容用 VHDL 语言和原理图分别完成设计、仿真和下载基本逻辑门电路半加器的过程:输入:a,b ; 输出:求和 sum,进位 c;三、实验设备1. KH-31001 主机 ;2. KH-33001/2/3 下载板(或 KH-33004 下载板 或 KH-33005 下载板);四、实验步骤1. 新建文本文件 在 Quartus Ⅱ 管理器界面中选择 File/New.., 菜单,出现 New 对话框,如图 1.1 所示。在对话框中选择VHDL File,点击 OK,打开文本编辑器,输入半加器的 VHDL 语言程序,如图 1.2 所示。然后保存文件halfadd.vhd。需要注意的是,文件名与模块名必须一致。图 1.1 Quartus Ⅱ 新建文本文件界面图 1.2 输入半加器的 VHDL 语言程序2.建立工程项目精品文档---下载后可任意编辑(1)在管理器窗口中选择 File/New Project Wizard...菜单,出现新建项目向导 New Project Wizard 对话框,输入项目目录(r:\test)、项目名称(halfadd)和顶层实体(halfadd),如图 1.4 所示,顶层实体名可以与项目名不同。图 1.4 建立工程项目(2)点击 Next,“…”添加文件对话框。点击按钮,添加与该项目有关的所有文件到当前项目,如图 1.5 所示。本例只有一个文件 halfadd.vhd,所以不用添加其它器件。精品文档---下载后可任意编辑图 1.7 添加项目有关的文件(3)点击 Next 按钮,再点击 Next 选择目标器件系列 ACEX1K,选择目标器件封装形式,引脚数目和速度级别。如图 1.8 所示,点击 NEXT。图 1.8 选择目标器件(4)点击 FINISH 按钮,项目 halfadd 出现在项目导航窗口中,如图 1.9 所示。双击文件名,即可打开文件。图 1.9 打开文件精品文档---下载后可任意编辑3. 编译并综合 选择菜单 Processing\Start Complition 或直接点击工具栏中编译快捷按钮开始编译。编译过程中,状态窗口显示编译进度的百分比和每个阶段所花费的时间。信息窗口显示所有信息,警告和错误,双击某个信息项,可以定位到原设计文件并高亮显示。编译完成后将产生一个编译报告栏,编译结果在编译报告栏中自动更新,如图 1.10 所示。报告栏包含了将一个设计适配到器件的所有信息。选中某一项可获得更详细的信息。如编译有错误,需要修改设计进行,并重新编译。4. 设计仿真...