华中科技大学计算机学院 《数字电路与逻辑设计》试卷 A (闭卷) 班级 学号 姓名 成绩 一.单项选择题(每题 1分,共 10分) 1.表示任意两位无符号十进制数需要( )二进制数

A.6 B.7 C.8 D.9 2.余 3码 10001000对应的 2421码为( )

A.01010101 B

10000101 C

10111011 D

11101011 3.补码 1.1000的真值是( )

0111 B

0111 C

1001 D

1000 4.标准或-与式是由( )构成的逻辑表达式

A.与项相或 B

最小项相或 C

最大项相与 D

或项相与 5

根据反演规则, EDECCAF的反函数为( )

E)]ED(CC[AF B

E)ED(CCAF C

E)EDCCA(F D

E)(DAFECC 6.下列四种类型的逻辑门中,可以用( )实现三种基本运算

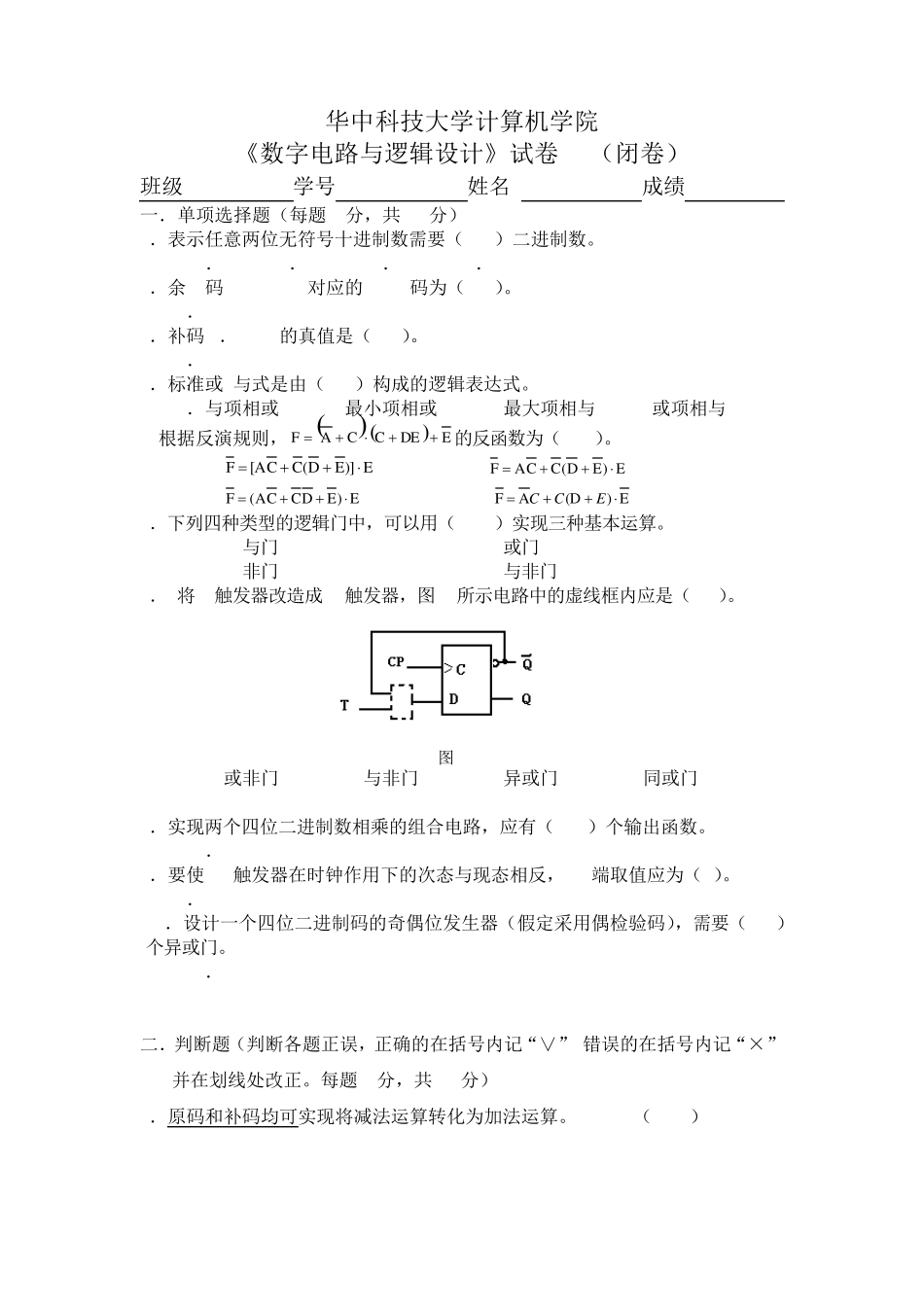

与非门 7. 将 D触发器改造成 T触发器,图 1所示电路中的虚线框内应是( )

同或门 8.实现两个四位二进制数相乘的组合电路,应有( )个输出函数

A. 8 B

11 9.要使 JK触发器在时钟作用下的次态与现态相反, JK端取值应为( )

A.JK=00 B

JK=01 C

JK=10 D

JK=11 10.设计一个四位二进制码的奇偶位发生器(假定采用偶检验码),需要( )个异或门

5 二.判断题(判断各题正误,正确的在括号内记“∨”,错误的在括号内记“×”,并在划线处改正

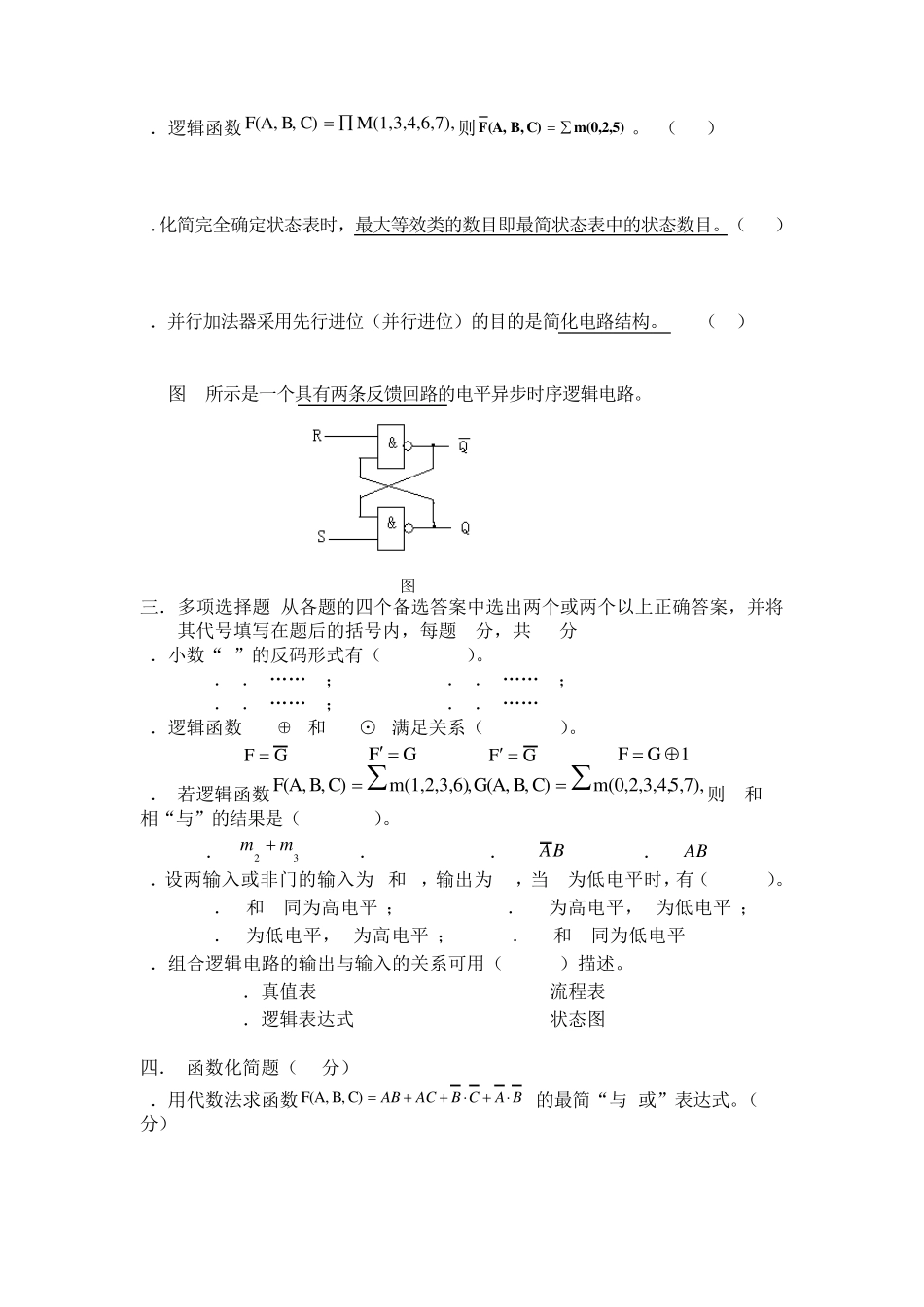

每题 2分,共 10分) 1.原码和补码均可实现将减法运算转化为加法