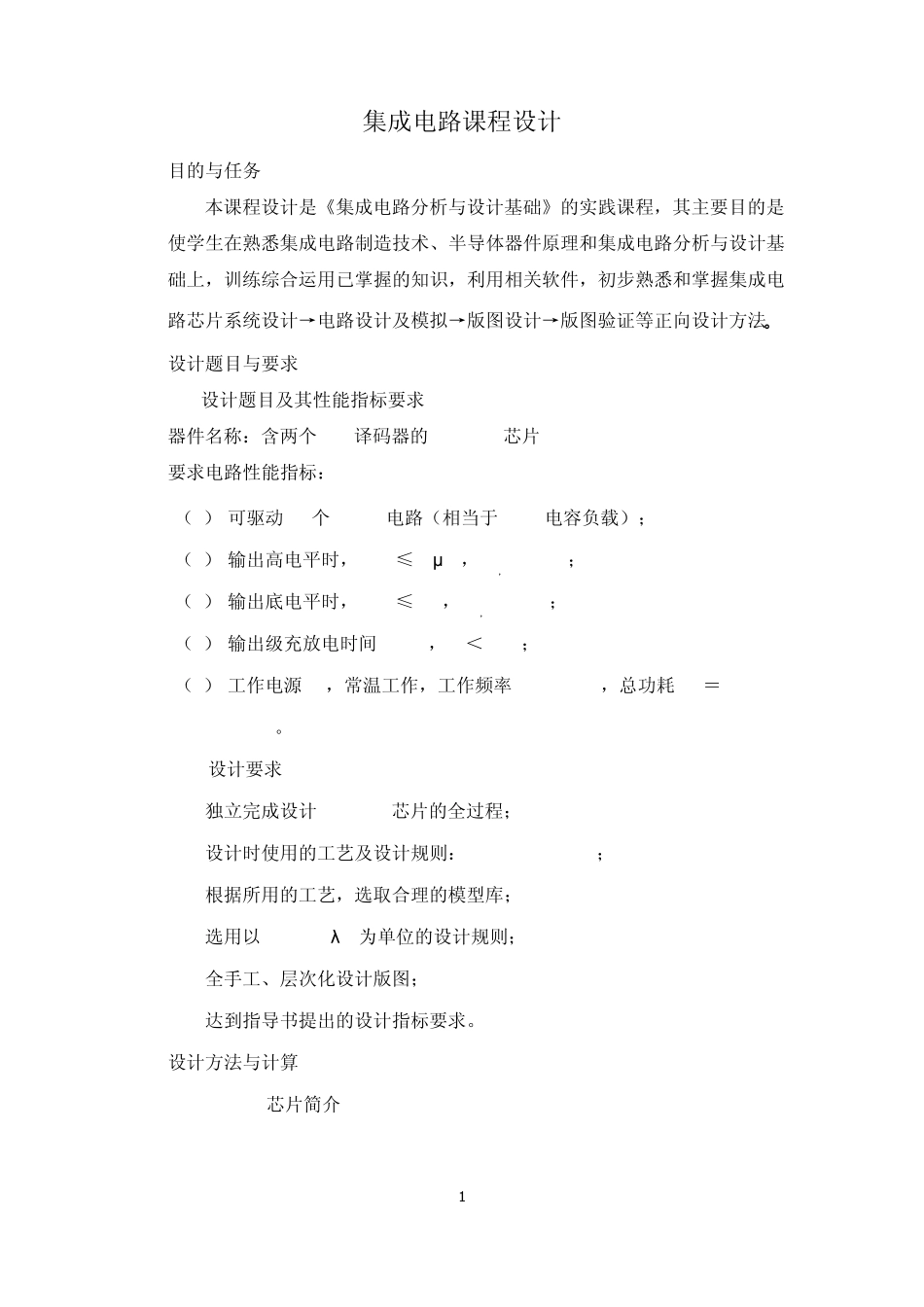

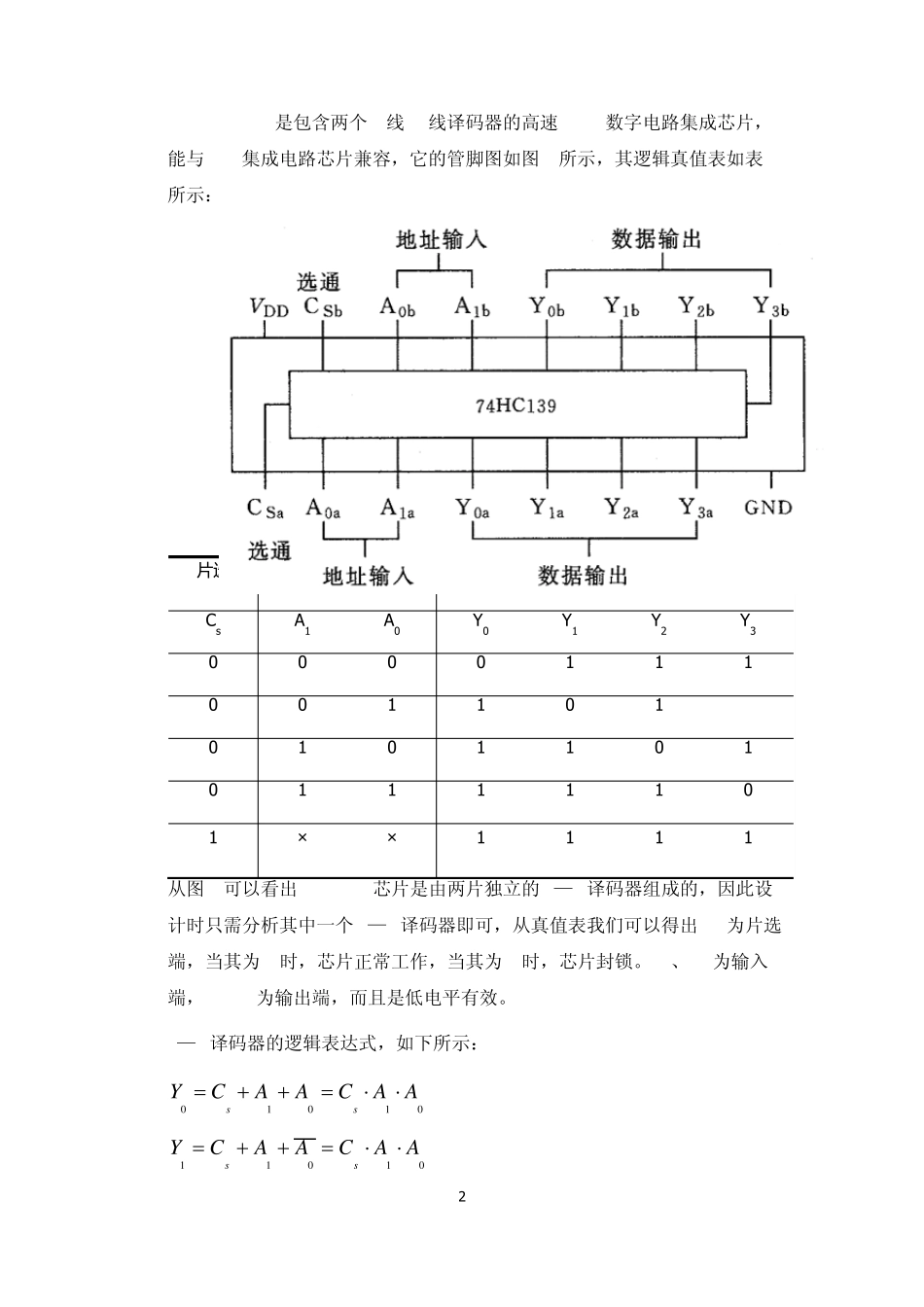

1 集成电路课程设计 1. 目的与任务 本课程设计是《集成电路分析与设计基础》的实践课程,其主要目的是使学生在熟悉集成电路制造技术、半导体器件原理和集成电路分析与设计基础上,训练综合运用已掌握的知识,利用相关软件,初步熟悉和掌握集成电路芯片系统设计→电路设计及模拟→版图设计→版图验证等正向设计方法。 2. 设计题目与要求 2.1设计题目及其性能指标要求 器件名称:含两个 2-4译码器的74HC139芯片 要求电路性能指标: (1) 可驱动 10个 LSTTL电路(相当于 15pF电容负载); (2) 输出高电平时,|IOH|≤20μ A,VOH,min=4.4V; (3) 输出底电平时,|IOL|≤4mA,VOL,man=0.4V; (4) 输出级充放电时间 tr=tf ,tpd<25ns; (5) 工作电源 5V,常温工作,工作频率 fwork=30MHz,总功耗 Pmax=150mW。 2.2设计要求 1. 独立完成设计74HC139芯片的全过程; 2. 设计时使用的工艺及设计规则: MOSIS:mhp_n12; 3. 根据所用的工艺,选取合理的模型库; 4. 选用以 lambda(λ )为单位的设计规则; 5. 全手工、层次化设计版图; 6. 达到指导书提出的设计指标要求。 3. 设计方法与计算 3.1 74HC139芯片简介 2 74HC139是包含两个2线-4线译码器的高速CMOS数字电路集成芯片,能与TTL集成电路芯片兼容,它的管脚图如图1所示,其逻辑真值表如表1所示: 图1 74HC139芯片管脚图 表1 74HC139真值表 片 选 输 入 数 据 输 出 Cs A1 A0 Y0 Y1 Y2 Y3 0 0 0 0 1 1 1 0 0 1 1 0 1 0 1 0 1 1 0 1 0 1 1 1 1 1 0 1 × × 1 1 1 1 从图1可以看出74HC139芯片是由两片独立的2—4译码器组成的,因此设计时只需分析其中一个2—4译码器即可,从真值表我们可以得出Cs为片选端,当其为 0时,芯片正常工作,当其为 1时,芯片封锁。A1、A0为输入端,Y0-Y3为输出端,而且是低电平有效。 2—4译码器的逻辑表达式,如下所示: 01010AACAACYss 01011AACAACYss 3 01012AACAACYss 01013AACAACYss 74HC139的逻辑图如图2所示: 图2 74HC139逻辑图 3.2 电路设计 本次设计采用的是m12_20的模型库参数进行各级电路的尺寸计算,其参数如下: NMOS: ε ox=3.9×8.85×10﹣12F/m μ n=605.312×10﹣4㎡/Vs tox=395×10﹣10m Vtn=0.81056V PMOS: ε ox=3.9×8.85×10﹣12F/m μ p=219×10﹣4㎡...