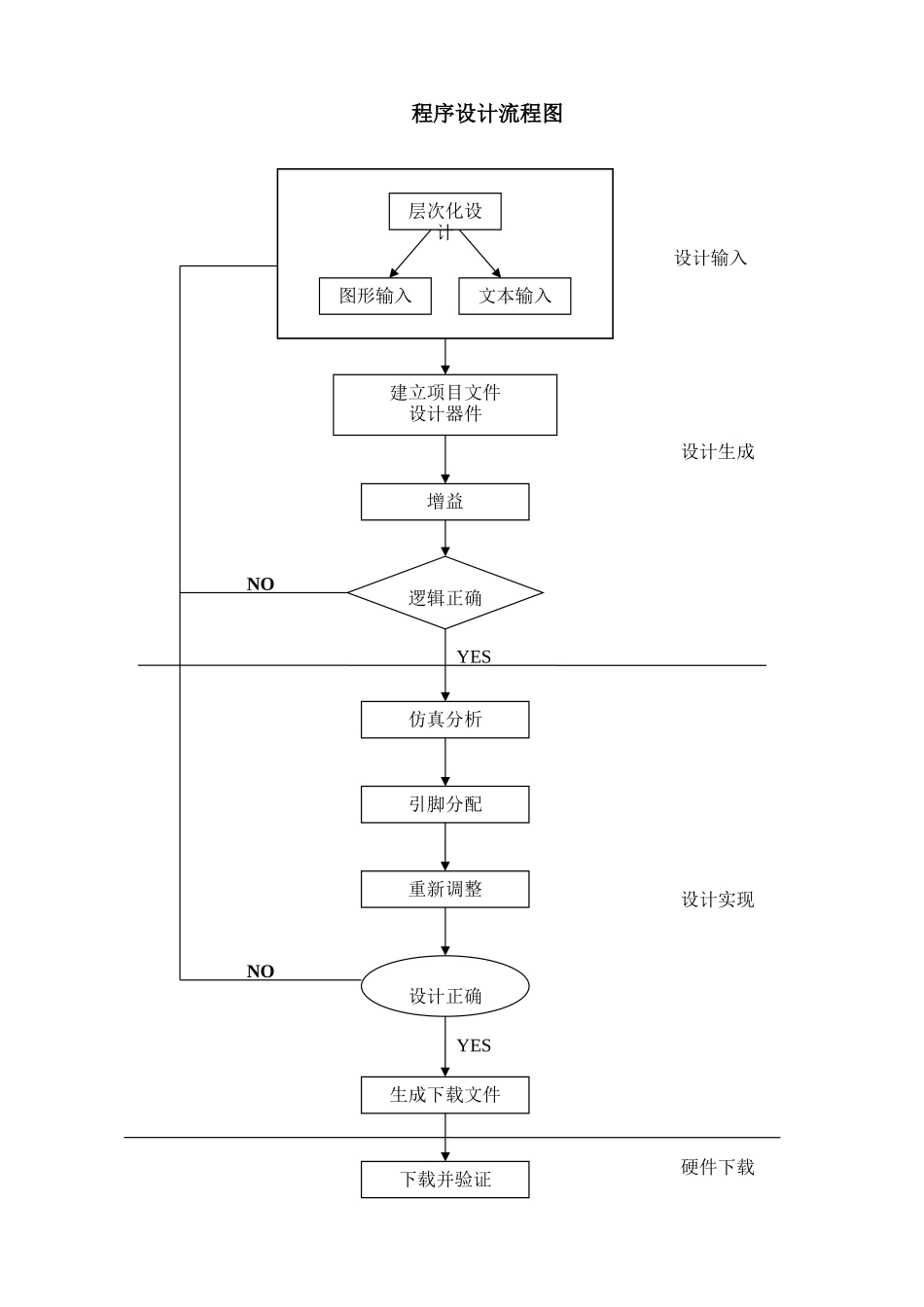

目 录目录 1一、方案设计与论证 4二、单元电路设计 5(一)抢答鉴别模块 5(二)计时模块 7(三)数据选择模块 9(四)报警模块 11(五)译码模块 13(六)分频模块 14(七)顶层文件 16(八)主电路连线图 19(九)将程序下载到芯片 FLEX—EPF10LC84-4 上,引脚图如下 19三、器件编程与下载 20四、性能测试与分析 20五、实验设备 20六、心得体会 21七、参考文献 21层次化设计图形输入文本输入建立项目文件设计器件增益逻辑正确仿真分析引脚分配重新调整设计正确生成下载文件下载并验证NONOYESYES设计输入设计生成设计实现硬件下载程序设计流程图一、方案设计与论证将该任务分成七个模块进行设计,分别为:抢答器鉴别模块、抢答器计时模块、抢答器记分模块、分频模块、译码模块、数选模块、报警模块,最后是撰写顶层文件。1、 抢答器鉴别模块:在这个模块中主要实现抢答过程中的抢答功能,并能对超前抢答进行警告,还能记录无论是正常抢答还是朝前抢答者的台号,并且能实现当有一路抢答按键按下时,该路抢答信号将其余个绿抢答封锁的功能。其中有四个抢答信号s0、s1、s2、s3;抢答使能信号 s;抢答状态显示信号 states;抢答与警报时钟信号 clk2;系统复位信号 rst;警报信号 tmp。2、 抢答器计时模块:在这个模块中主要实现抢答过程中的计时功能,在有抢答开始后进行 30 秒的倒计时,并且在 30 秒倒计时后无人抢答显示超时并报警。其中有抢答时钟信号clk2;系统复位信号 rst;抢答使能信号 s;抢答状态显示信号 states;无人抢答警报信号 warn;计时中止信号 stop;计时十位和个位信号 tb,ta。3、 数据选择模块:在 这 个 模 块 中 主 要 实 现 抢 答 过 程 中 的 数 据 输 入 功 能 , 输 入 信 号a[3..0]、b[3..0]、c[3..0];计数输出信号 s;数据输出信号 y;计数脉冲clk2,实现 a、b、c 按脉冲轮流选通,在数码管上显示。4、 报警模块: 在这个模块中主要实现抢答过程中的报警功能,当主持人按下控制键,有限时间 人抢答或是计数到时蜂鸣器开始报警,有效电平输入信号 i;状态输出信号 q;计数脉冲 clk2。5、 译码模块:在这个模块中主要实现抢答过程中将 BCD 码转换成 7 段的功能。6、 分频模块:在这个模块中主要实现抢答过程中实现输出双脉冲的功能。7、 顶层文件:在这个模块中是对前七个模块的综合编写的顶层文件。抢答器的设计分析根据要求,我们可...