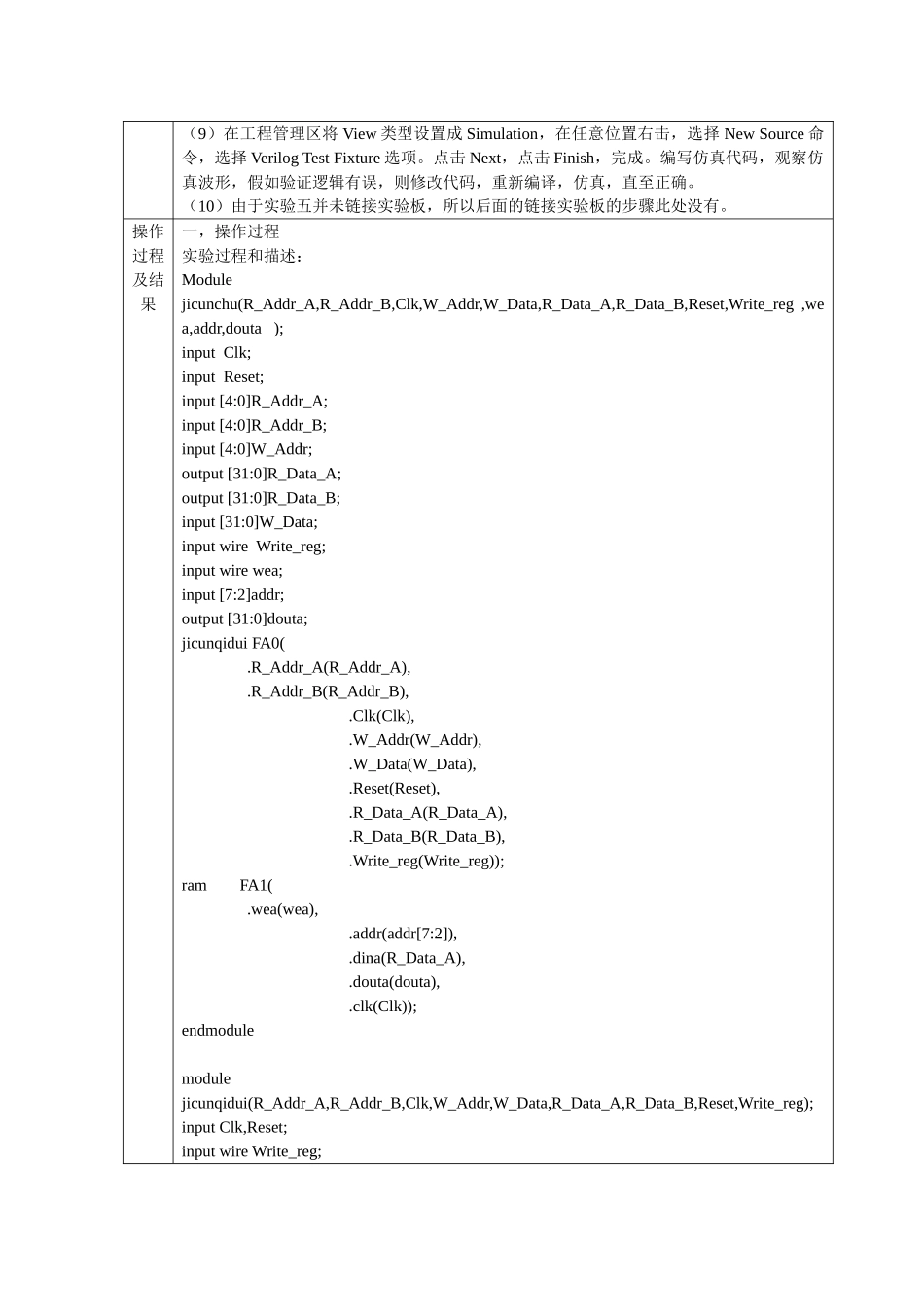

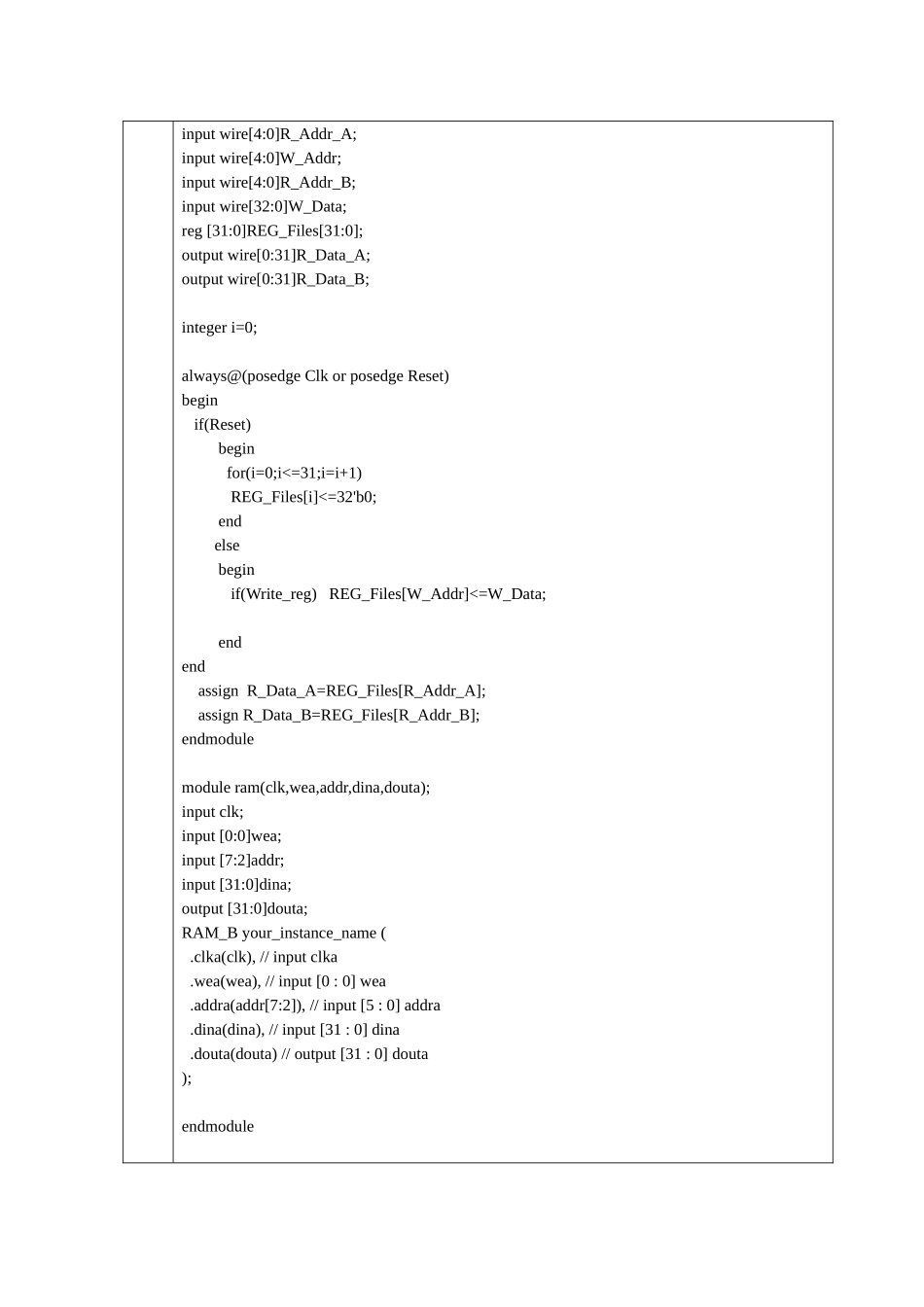

杭州电子科技大学计算机学院实验报告实验项目: 课程名称:计算机组成原理与系统结构设计姓名: 学号: 同组姓名: 学号: 实验位置(机号): 实验日期: 指导老师: 实验内容(算法、程序、步骤和方法)一、实验目的(1)掌握灵活应用 Verilog HDL 进行各种描述与建模的技巧和方法。(2)学习在 ISE 中设计生成 M 恶魔人员 IP 核的方法。(3)学习存储器的结构及读写原理,掌握存储器的设计方法。二、实验仪器 ISE 工具软件三、步骤、方法(1)在 ISE 的工程目录里生成一个扩展名为 Test_Mem.coe。该文件是用于 Memory IP 核的初始化文件。文件包括两行,memory_initialization_radix=16;memory_initialization_vector=00000820,00632025,00010fff,20006789,FFFF0000,0000FFFF,88888888,99999999,aaaaaaaa,bbbbbbbb;(2)启动 ISE 工具软件,选择 File->New Project,输入工程名 shiyan5,默认选择后,点击Next 按钮,确认工程信息后点击 Finish 按钮,创建一个完整的工程(3)在工程管理区的任意位置右击,选择 New Source 命令。弹出 New Source Wizard 对话框,选择 IP(CORE Generator&Architecture Wizard),并输入存储器 IP 核的名称 RAM_B,点击 Next 按钮进入下一步,在 IP 核选择界面,选择 Memories&Storage Elements 下的Block Memory Generator 选项,单击 next 按钮,点击 Finish 进入参数设置。(4)Memory IP 参数设置。在第 1 页选择默认接口:Native.第 2 页选择 Memory Type 为Single Port RAM.第三页修改 Write Width 为 32,Write Depth 为 64.选择 Always Enabled。第4 页选中 Load Init File,选择第一步生成的 COE 文档。第 5 页和第 6 页默认无需修改。单击 Generate 按 钮 , 系 统 将 在 工 程 管 理 区 生 成 一 个 RAM_B 存 储 器 模 块 :RAM_B(RAM_B.xco)。之后在过程管理区会出现核生成器菜单。(5)调用 RAM_B 模块:双击过程管理区的 View HDL Instruction Template,右侧代码区出现 RAM_B 的调用模板。(6)在工程管理区的任意位置右击,选择 New Source 命令。弹出 New Source Wizard 对话框,选择 Verilog Module,并输入 Verilog 文件名 ram,点击 Next 按钮进入下一步,点击Finish 完成创建。将 RAM_B 的调用模板粘贴过来。并对 ram 进行仿真。(7)在工程...