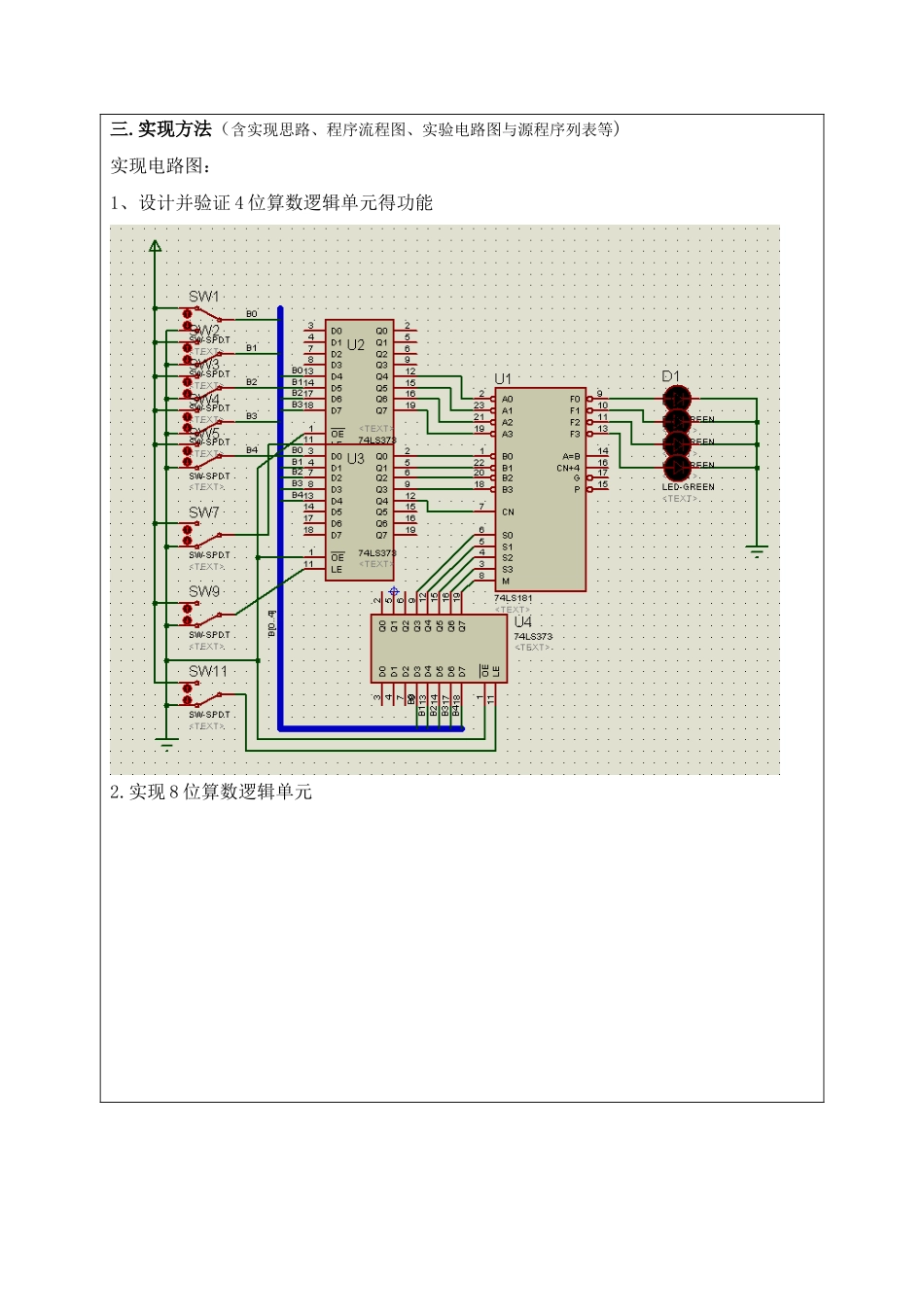

成绩:计算机原理实验室实验报告课 程 : 计算机组成原理 姓 名 : 姜香玉 专 业 : 网络工程 学 号 : 132055 2 15 日 期 : 20 15 年 1 2月 太原工业学院计算机工程系实验一:运算器实验实验环境PC 机+Wi n 2025+emu8086+pr o teus 仿真器实验日期2025 年、10一.实验内容1.熟悉pr oteus 仿真系统2.设计并验证 4 位算数逻辑单元得功能3.实现输入输出锁存4.实现 8 位算数逻辑单元二.理论分析或算法分析实验原理:算术逻辑运算单元得核心就是由 74L S 181 构成,它可以进行二进制数得算术逻辑运算,74L S1 8 1 得各种工作方式可通过设置其控制信号来实现。当正确设置 74L S1 8 1 得各个控制信号,74L S 181 会运算数据锁存器内得数据。由于数据锁存器已经把数据锁存,只要 74 L S1 81得控制信号不变,那么 74LS 18 1 得输出数据也不会发生改变。输出缓冲器采纳 74LS245,当控制信号为低电平常,74 LS 24 5导通,把7 4L S1 81 得运算结果输出到数据总线,高电平常,7 4LS245 得输出为高阻.实验中所用得运算器数据通路如图所示.其中运算器由两片7 4LS 1 81 以并/串形式构成8位字长得 AL U.运算器得输出经过一个三态门(74L S245)以 8 芯扁平线方式与数据总线相连,运算器得2个数据输入端分别由二个锁存器(74LS2 7 3)锁存,锁存器得输入亦以8芯扁平线方式与数据总线相连,数据开关(IN P U T DEVIC E)用来给出参加运算得数据,经一三态门(7 4 L S2 4 5)以 8 芯扁平线方式与数据总线相连,数据显示灯(BUS UNIT)已与数据总线相连,用来显示数据总线内容.三.实现方法(含实现思路、程序流程图、实验电路图与源程序列表等)实现电路图:1、设计并验证 4 位算数逻辑单元得功能2.实现 8 位算数逻辑单元四.实验结果分析(含执行结果验证、输出显示信息、图形、调试过程中所遇得问题及处理方法等)(一)验证了基本要求,实现了设计并验证 4 位算数逻辑单元、实现输入输出锁存、实现 8 位算数逻辑单元得功能、运行结果:图一图二:(二)思考问题:单总线,双总线与三总线结构在设计上得异同答:单总线结构:对这种结构得运算器来说,在同一时间内,只能有一个操作数放在单总线上。为了把两个操作数输入到 A LU,需要分两次来做,而且还需要 A,B 两个缓冲寄存器。这种结构得主要缺点就是操作速度较慢。...