可校时的数字钟(6 页)Good is good, but better carries it

精益求精,善益求善

一、 设计题目多功能数字电子钟二、 设计目的1、掌握数字电路中计数、分频、译码、显示及时钟脉冲振荡器等组合逻辑电路与时序逻辑电路的综合应用

2、掌握多功能数字钟电路设计方法、装调技术及数字钟的扩展应用

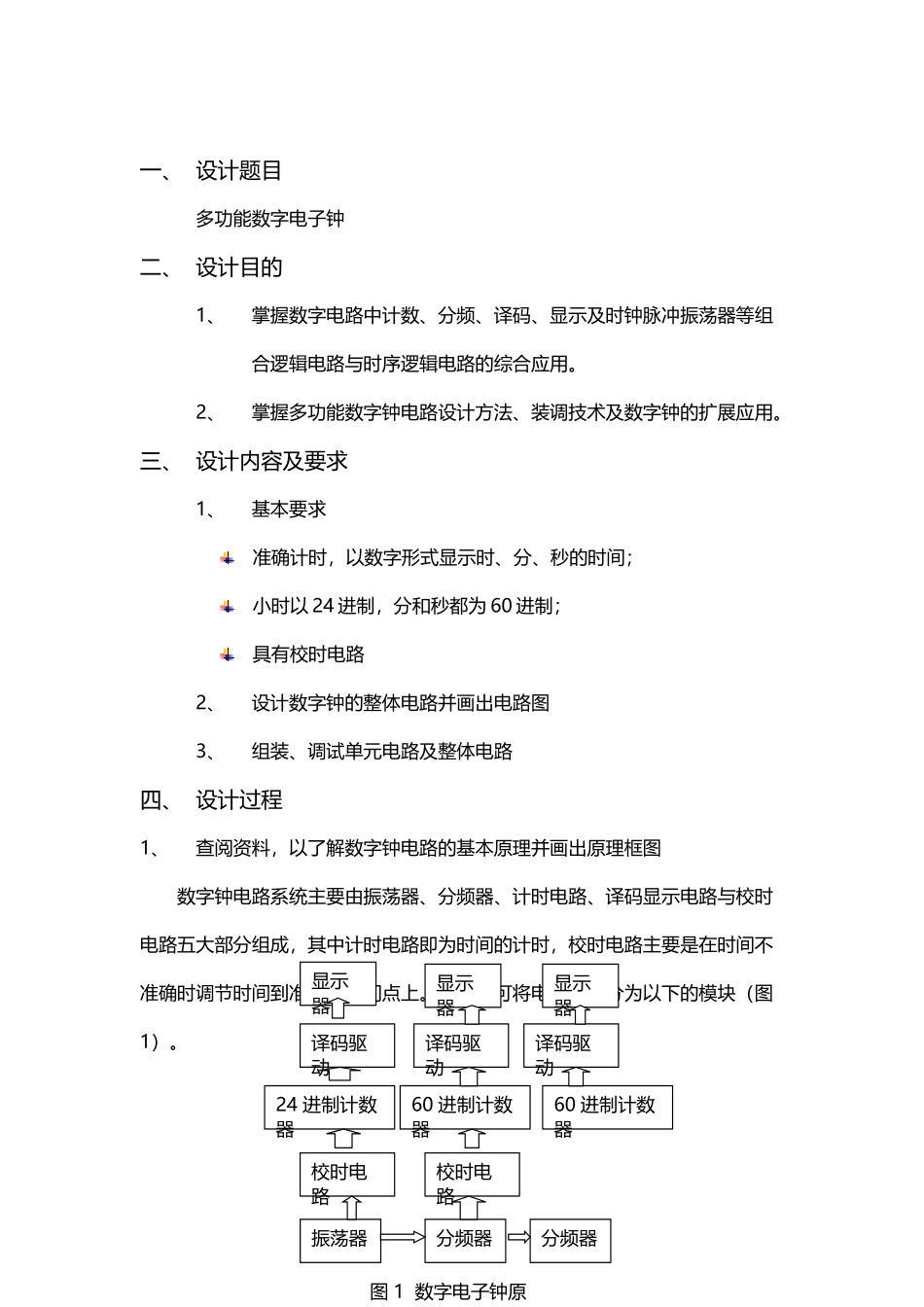

三、 设计内容及要求1、基本要求准确计时,以数字形式显示时、分、秒的时间;小时以 24 进制,分和秒都为 60 进制;具有校时电路2、设计数字钟的整体电路并画出电路图3、组装、调试单元电路及整体电路四、 设计过程1、查阅资料,以了解数字钟电路的基本原理并画出原理框图数字钟电路系统主要由振荡器、分频器、计时电路、译码显示电路与校时电路五大部分组成,其中计时电路即为时间的计时,校时电路主要是在时间不准确时调节时间到准确的时间点上

因此,可将电路系统分为以下的模块(图1)

显示器显示器显示器译码驱动译码驱动译码驱动24 进制计数器60 进制计数器60 进制计数器校时电路校时电路振荡器分频器分频器图 1 数字电子钟原理由以上的模块图可知,本电路主要由振荡器和分频器产生 1HZ(即 1 秒)的秒脉冲,用秒脉冲驱动计数器开始计时

因为每分钟 60 秒,每小时 60 分钟,所以应该有 24 进制的“时计数器”、60 进制的“分计数器”、60 进制的“秒计数器”

当“秒计数器”计数到 59 后,下一个脉冲一到“分计数器”就进1,“分计数器”计数到 59 后,再来一个脉冲“时计数器”就进 1

秒计数器的输出经译码、显示时钟秒

分计数器的输出经译码、显示时钟分

时计数器的输出经译码、显示时钟时

因每天有 24 小时,当计数到 23:59:59 时,再来一个脉冲后,就显示 00:00:00

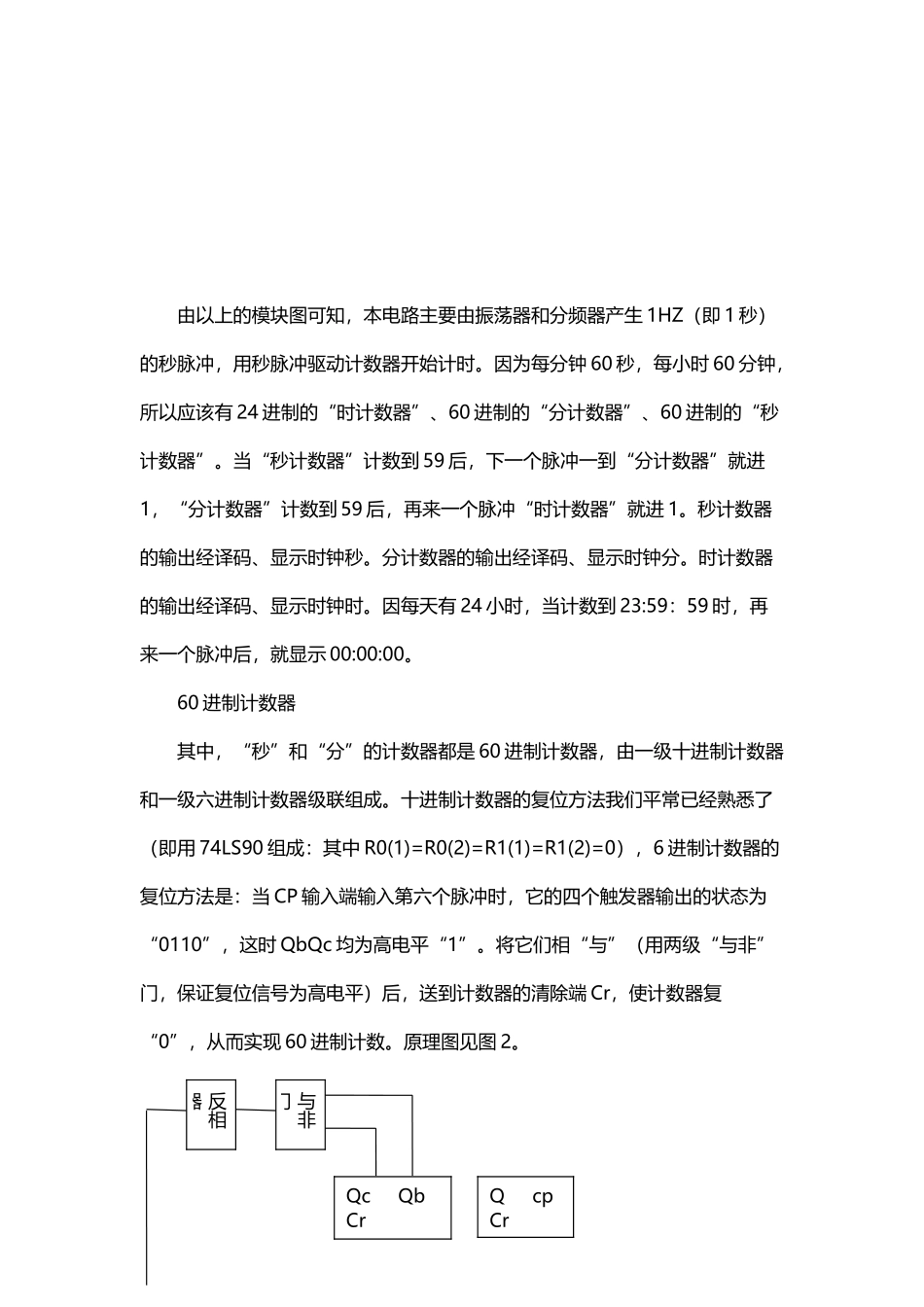

60 进制计数器其中,“秒”和“分”的计数器都是 60 进制计数器,由一级十进制计数器和一级六