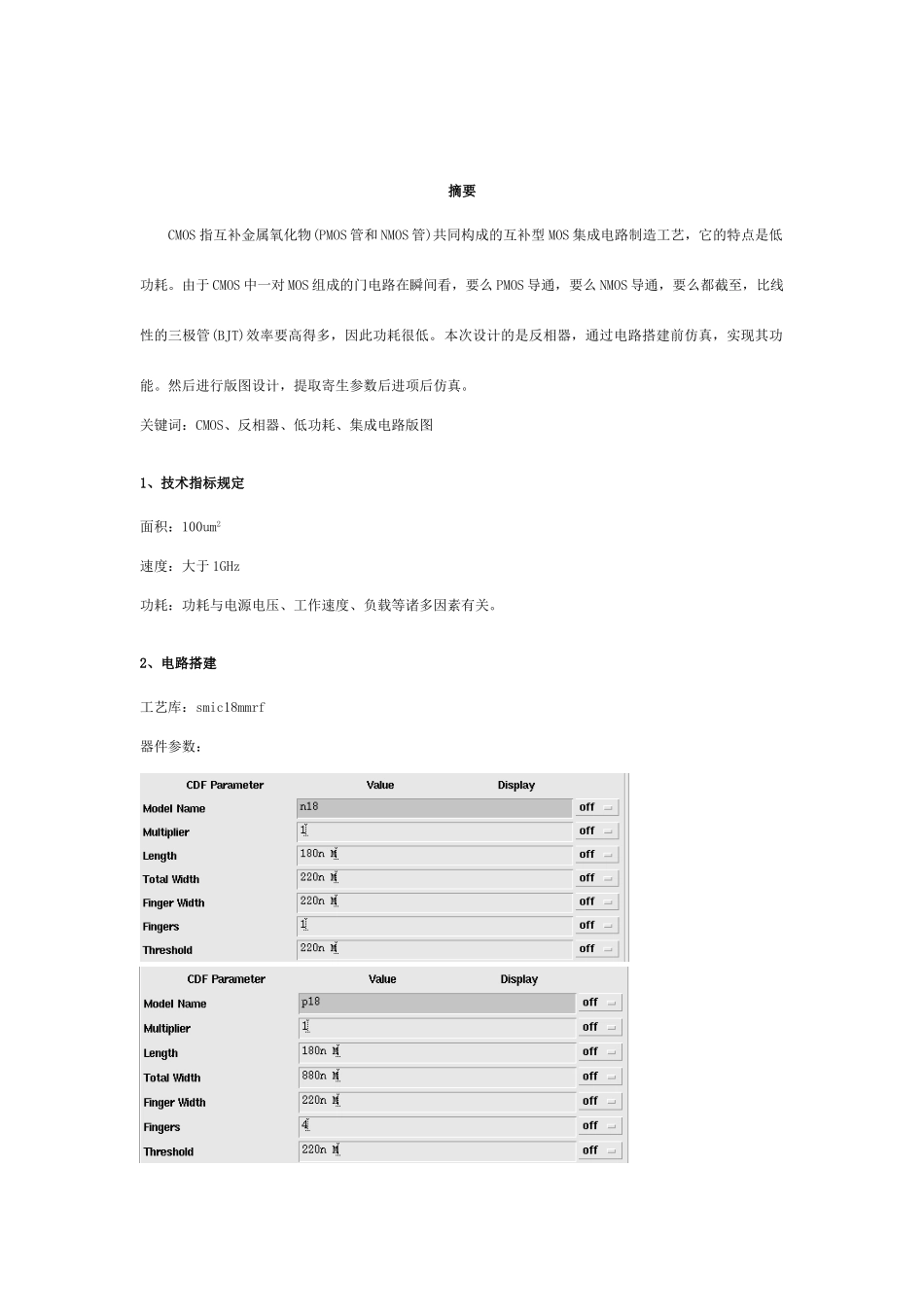

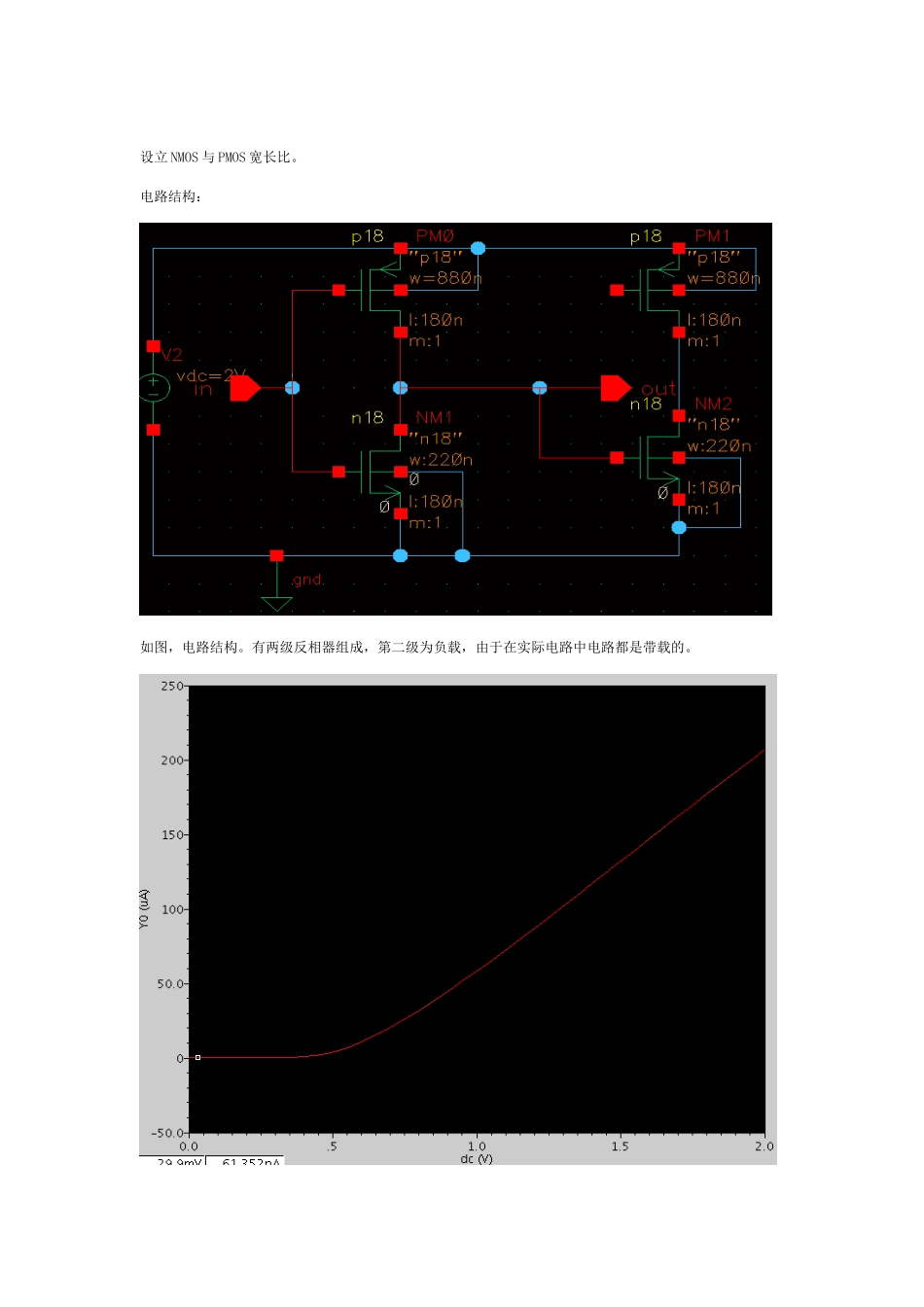

题目:反相器分析与设计姓名:白进宝学院:微电子与固体电子学院学号:署名:老师署名:摘要 CMOS 指互补金属氧化物(PMOS 管和 NMOS 管)共同构成的互补型 MOS 集成电路制造工艺,它的特点是低功耗。由于 CMOS 中一对 MOS 组成的门电路在瞬间看,要么 PMOS 导通,要么 NMOS 导通,要么都截至,比线性的三极管(BJT)效率要高得多,因此功耗很低。本次设计的是反相器,通过电路搭建前仿真,实现其功能。然后进行版图设计,提取寄生参数后进项后仿真。关键词:CMOS、反相器、低功耗、集成电路版图1、技术指标规定面积:100um2速度:大于 1GHz功耗:功耗与电源电压、工作速度、负载等诸多因素有关。2、电路搭建工艺库:smic18mmrf器件参数:设立 NMOS 与 PMOS 宽长比。电路结构:如图,电路结构。有两级反相器组成,第二级为负载,由于在实际电路中电路都是带载的。 分别作 NMOS 和 PMOS 的直流输出特性曲线,NMOS 的阈值电压大约为 0.5V 左右,PMOS 的阈值电压大约为0.6V 左右。3、仿真(1)进行直流传输特性仿真分析图一电源电压为 5V,图二电源电压为 2V。可以看到图二的特性比图一好,这是由于减少的电压,从而使特性变好。继续减少电源电压为 1V 后,特性更好。但是当降到 200mV 时,特性反而变差。这是由于当电压降到接近于阈值电压或更低时,管子无法导通,性能变差。 (2)瞬态特性分析瞬态特性分析,反相器实现非门的功能。将时间轴拉长,可以看到当输出反向时,存在一个过冲现象,这是由于栅漏电容导致。 (3)工作频率分析上图为反相器没有带负载的情况下测出的下降时间,下图为带一个反相器测出的下降时间。从而我们可以得出电路的扇出越多,性能越差,所以在数字电路中,我们尽量将扇出控制在 4 以内。更多的扇出将通过组合电路多级实现。 由图可得上升时间为 23.85ps,下降时间为 29.25ps。工作频率=1/(2×max(上升时间,下降时间))=17GHz(4)功耗分析如以上两幅图,分别在电源电压 5V 和 2V 的情况下动态电流分析。5V 时电流峰值为 1mA 左右,2V 时电流峰值为 300uA 左右。4、版图版图设计是将模拟优化后的电路转化成一系列几何图形,这些几何图形包含了集成电路尺寸大小、各层拓扑定义等有关元件的物理信息。如图为在 cadence 版图软件中绘制的反相器的版图。面积为 20um×10um=200um25、后仿真以上两幅图为后仿真的沟通仿真图。由图可得上升时间为 82.33ps,下降时间...