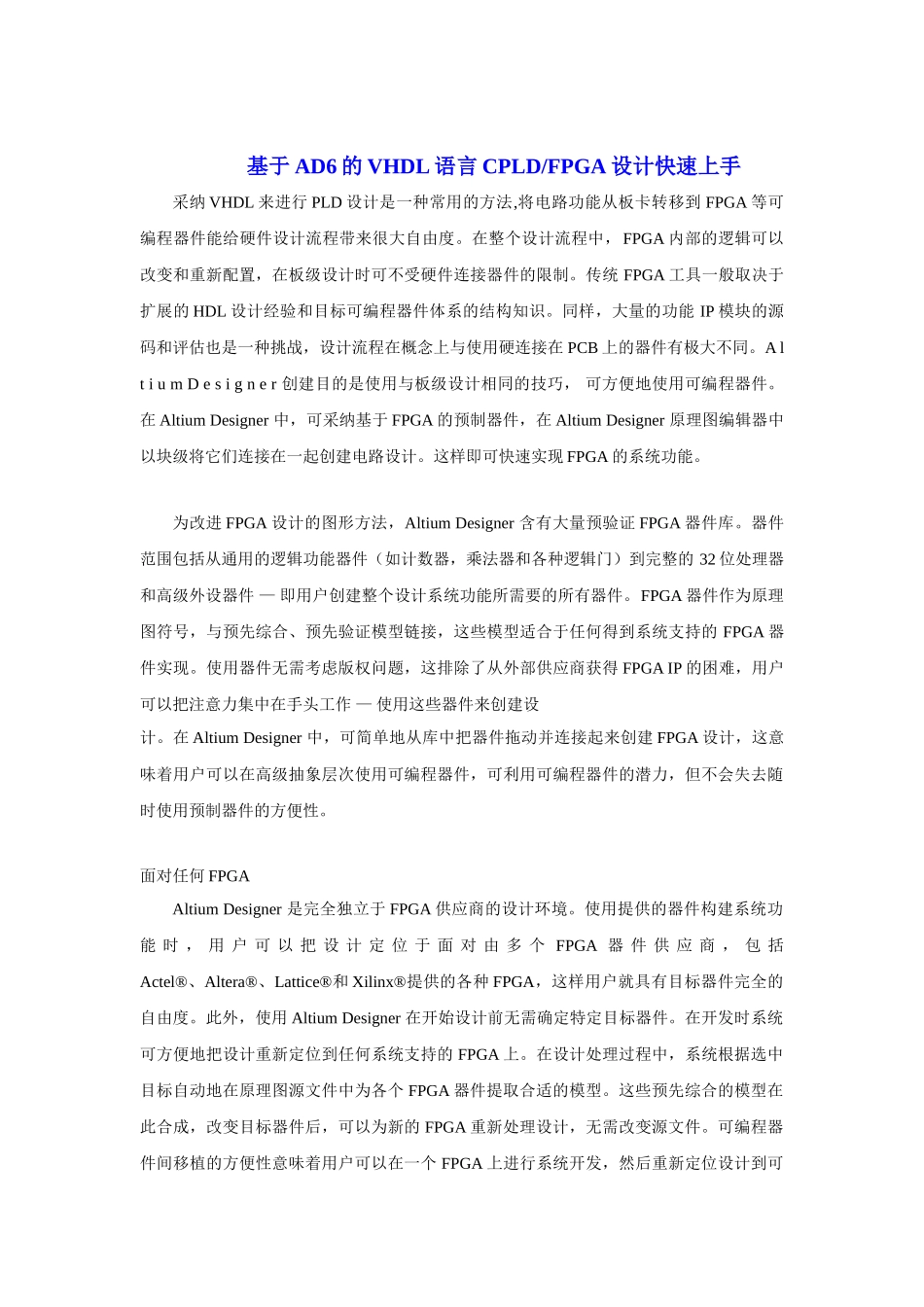

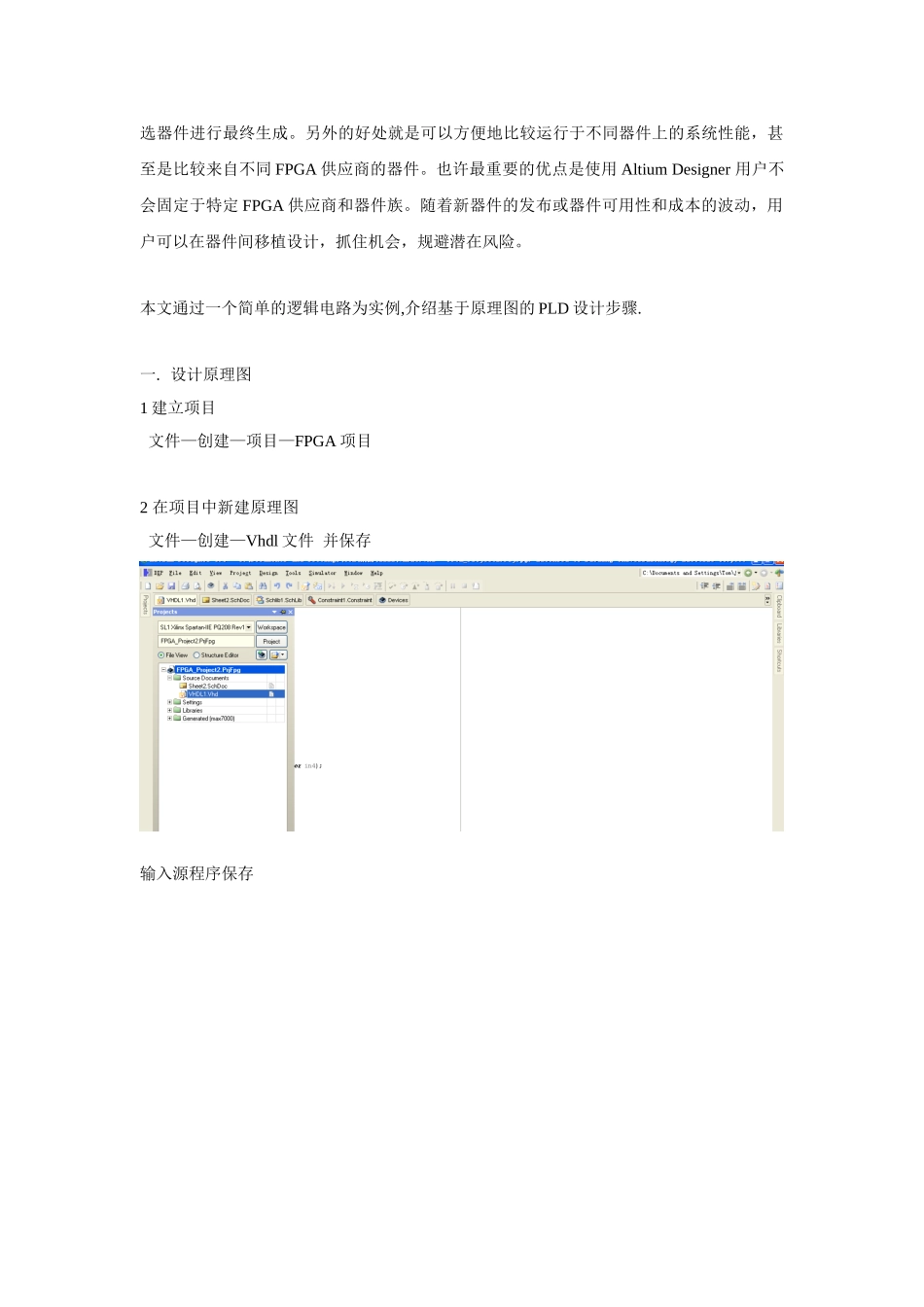

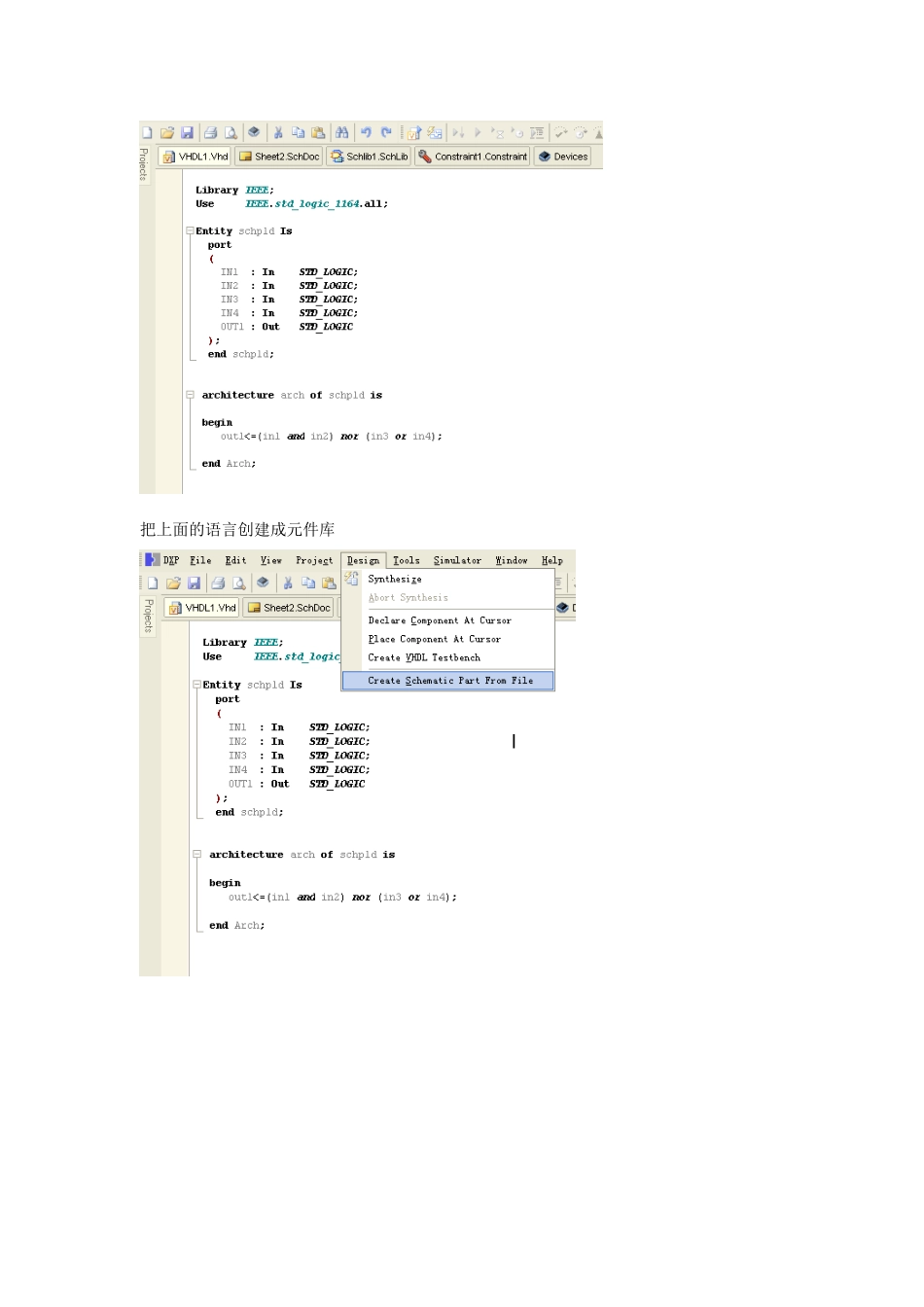

基于 AD6 的 VHDL 语言 CPLD/FPGA 设计快速上手采纳 VHDL 来进行 PLD 设计是一种常用的方法,将电路功能从板卡转移到 FPGA 等可编程器件能给硬件设计流程带来很大自由度。在整个设计流程中,FPGA 内部的逻辑可以改变和重新配置,在板级设计时可不受硬件连接器件的限制。传统 FPGA 工具一般取决于扩展的 HDL 设计经验和目标可编程器件体系的结构知识。同样,大量的功能 IP 模块的源码和评估也是一种挑战,设计流程在概念上与使用硬连接在 PCB 上的器件有极大不同。A l t i u m D e s i g n e r 创建目的是使用与板级设计相同的技巧, 可方便地使用可编程器件。在 Altium Designer 中,可采纳基于 FPGA 的预制器件,在 Altium Designer 原理图编辑器中以块级将它们连接在一起创建电路设计。这样即可快速实现 FPGA 的系统功能。为改进 FPGA 设计的图形方法,Altium Designer 含有大量预验证 FPGA 器件库。器件范围包括从通用的逻辑功能器件(如计数器,乘法器和各种逻辑门)到完整的 32 位处理器和高级外设器件 — 即用户创建整个设计系统功能所需要的所有器件。FPGA 器件作为原理图符号,与预先综合、预先验证模型链接,这些模型适合于任何得到系统支持的 FPGA 器件实现。使用器件无需考虑版权问题,这排除了从外部供应商获得 FPGA IP 的困难,用户可以把注意力集中在手头工作 — 使用这些器件来创建设计。在 Altium Designer 中,可简单地从库中把器件拖动并连接起来创建 FPGA 设计,这意味着用户可以在高级抽象层次使用可编程器件,可利用可编程器件的潜力,但不会失去随时使用预制器件的方便性。面对任何 FPGAAltium Designer 是完全独立于 FPGA 供应商的设计环境。使用提供的器件构建系统功能 时 , 用 户 可 以 把 设 计 定 位 于 面 对 由 多 个 FPGA 器 件 供 应 商 , 包 括Actel®、Altera®、Lattice®和 Xilinx®提供的各种 FPGA,这样用户就具有目标器件完全的自由度。此外,使用 Altium Designer 在开始设计前无需确定特定目标器件。在开发时系统可方便地把设计重新定位到任何系统支持的 FPGA 上。在设计处理过程中,系统根据选中目标自动地在原理图源文件中为各个 FPGA 器件提取合适的模型。这些预先综合的模型在此合成,改变目标器件后,可以为新的 FPGA 重新处理设计,无需改变源文件。可编程器件间移植的方便性意...