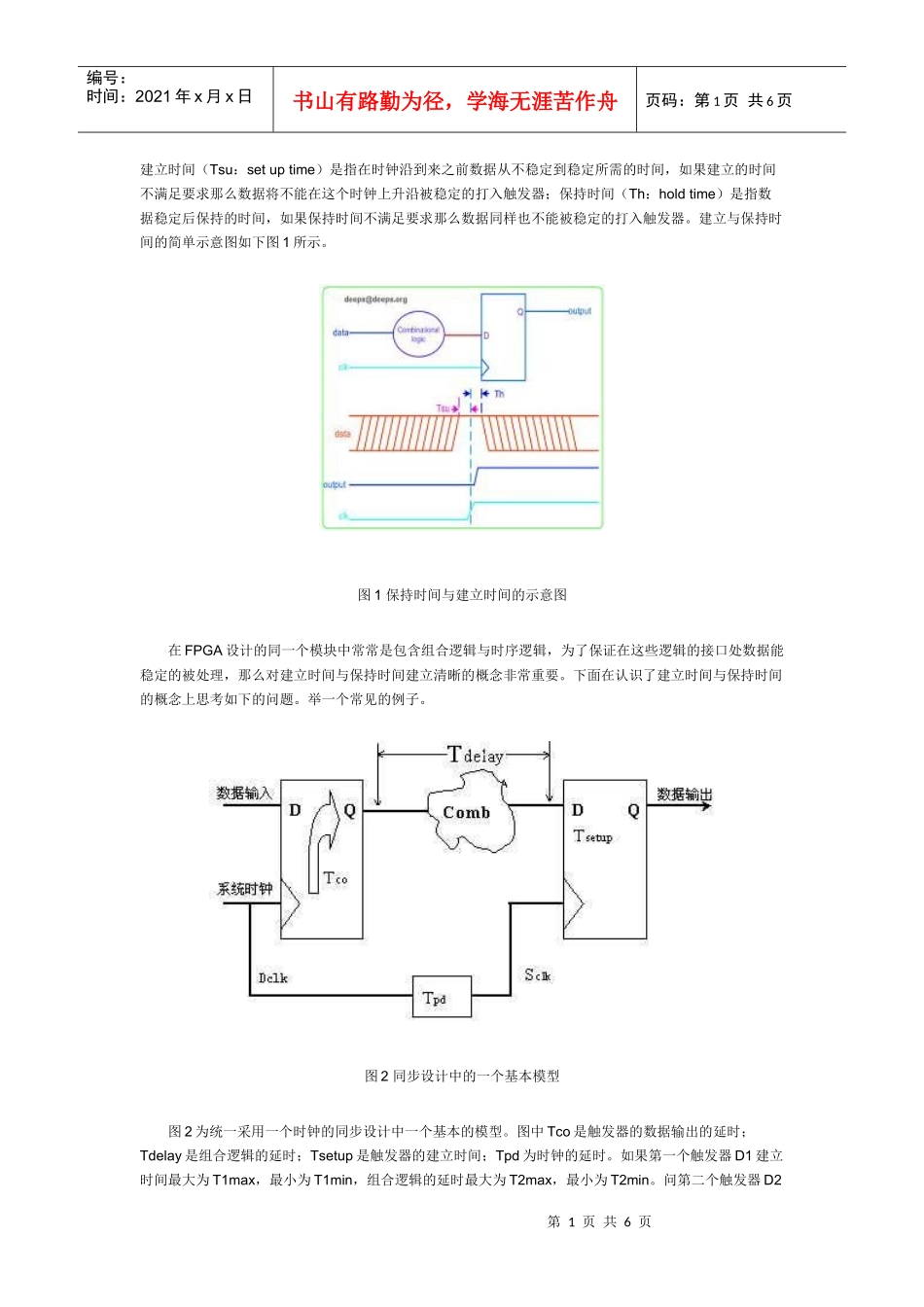

第1页共6页编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第1页共6页建立时间(Tsu:setuptime)是指在时钟沿到来之前数据从不稳定到稳定所需的时间,如果建立的时间不满足要求那么数据将不能在这个时钟上升沿被稳定的打入触发器;保持时间(Th:holdtime)是指数据稳定后保持的时间,如果保持时间不满足要求那么数据同样也不能被稳定的打入触发器

建立与保持时间的简单示意图如下图1所示

图1保持时间与建立时间的示意图在FPGA设计的同一个模块中常常是包含组合逻辑与时序逻辑,为了保证在这些逻辑的接口处数据能稳定的被处理,那么对建立时间与保持时间建立清晰的概念非常重要

下面在认识了建立时间与保持时间的概念上思考如下的问题

举一个常见的例子

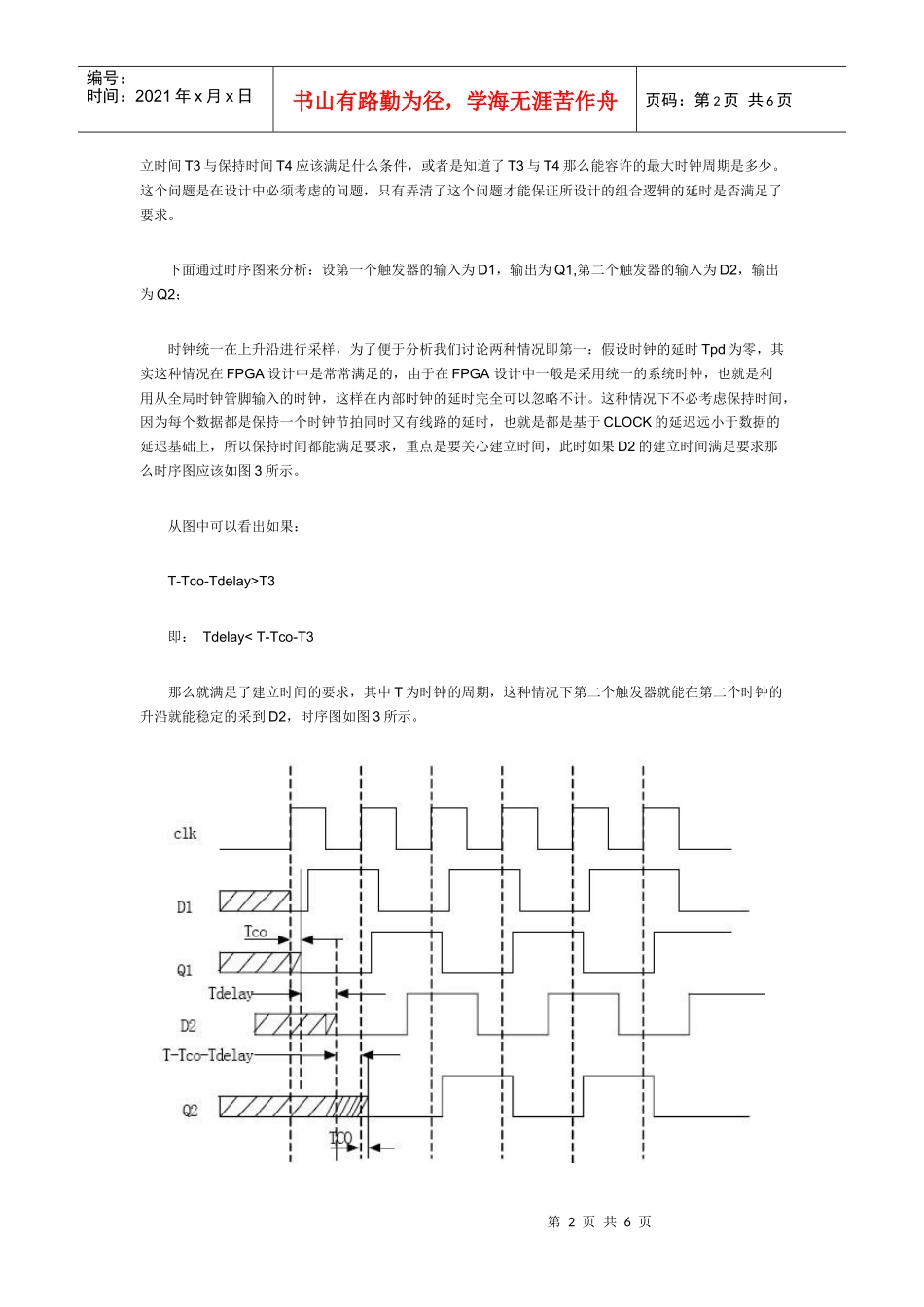

图2同步设计中的一个基本模型图2为统一采用一个时钟的同步设计中一个基本的模型

图中Tco是触发器的数据输出的延时;Tdelay是组合逻辑的延时;Tsetup是触发器的建立时间;Tpd为时钟的延时

如果第一个触发器D1建立时间最大为T1max,最小为T1min,组合逻辑的延时最大为T2max,最小为T2min

问第二个触发器D2第2页共6页第1页共6页编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第2页共6页立时间T3与保持时间T4应该满足什么条件,或者是知道了T3与T4那么能容许的最大时钟周期是多少

这个问题是在设计中必须考虑的问题,只有弄清了这个问题才能保证所设计的组合逻辑的延时是否满足了要求

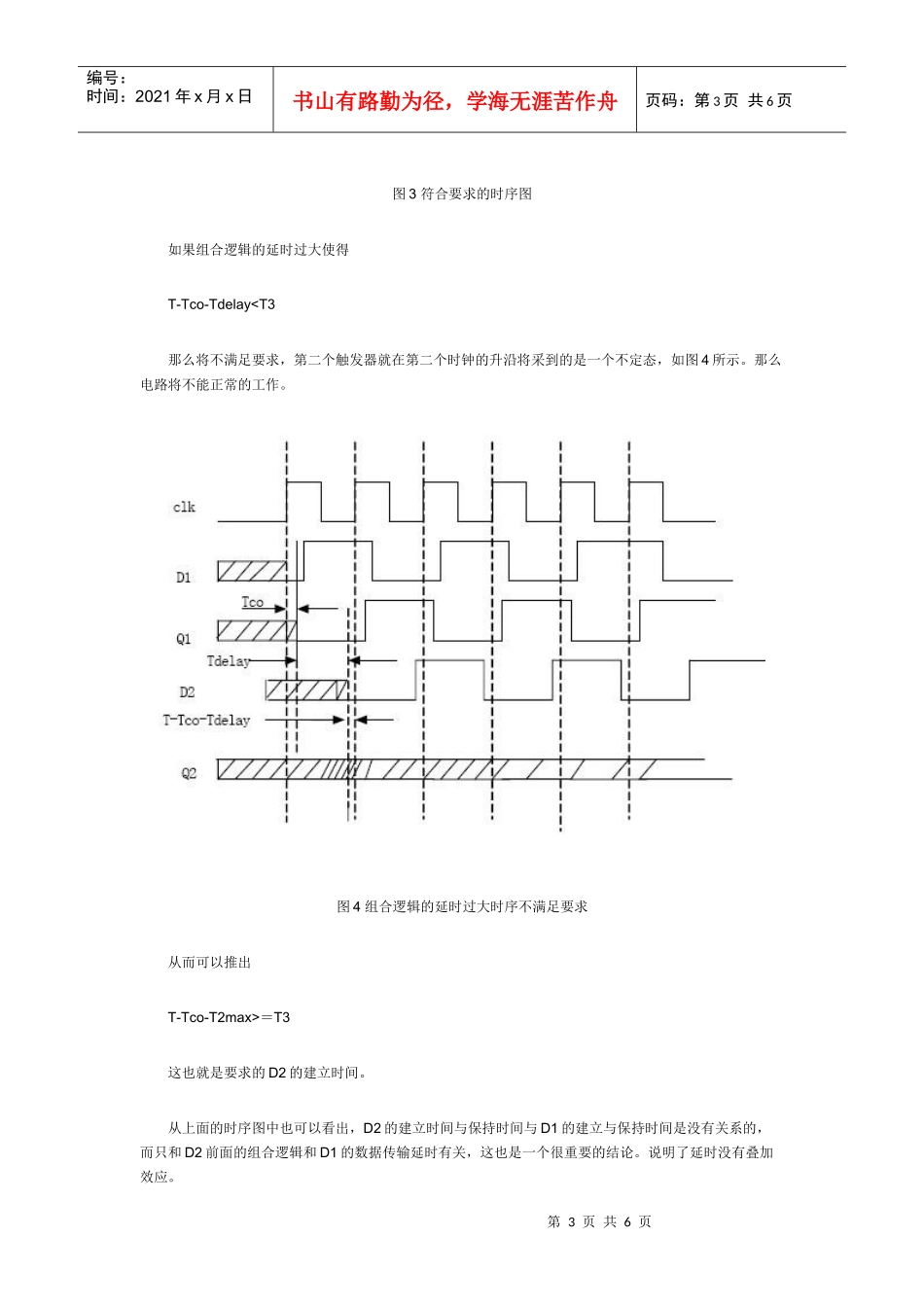

下面通过时序图来分析:设第一个触发器的输入为D1,输出为Q1,第二个触发器的输入为D2,输出为Q2;时钟统一在上升沿进行采样,为了便于分析我们讨论两种情况即第一:假设时钟的延时Tpd为零,其实这种情况在FPGA设计中是常常满足的,由于在FPGA设计中一般是采用统一的系统时钟,也就是利用从全局时钟管脚输入的时钟