第1页共8页编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第1页共8页电平简介――――内部培训资料(-)电平概述作为一个硬件设计工程师,了解我们现在常用器件的输入输出电平相关的知识是十分必要的

主要分为两大类,单端电平和双端电平

双端电平常用在传输高速信号的场合,以差分的形式在两条传输线上传送

单端电平常用在普通的信号线,一般速率不太高(通常指低于100MHz的传输速率)

对于双端电平,我们着重将在高速信号以及电平匹配的时候再作详细说明,这里先讨论单端的电平

单端的电平有很多种如:TTL、CMOS、LVTTL、LVCMOS、RS232、GTL、GTL+、HSTL、OC门、OD门等等

目前常用的单端电平主要有两种:TTL电平和CMOS电平

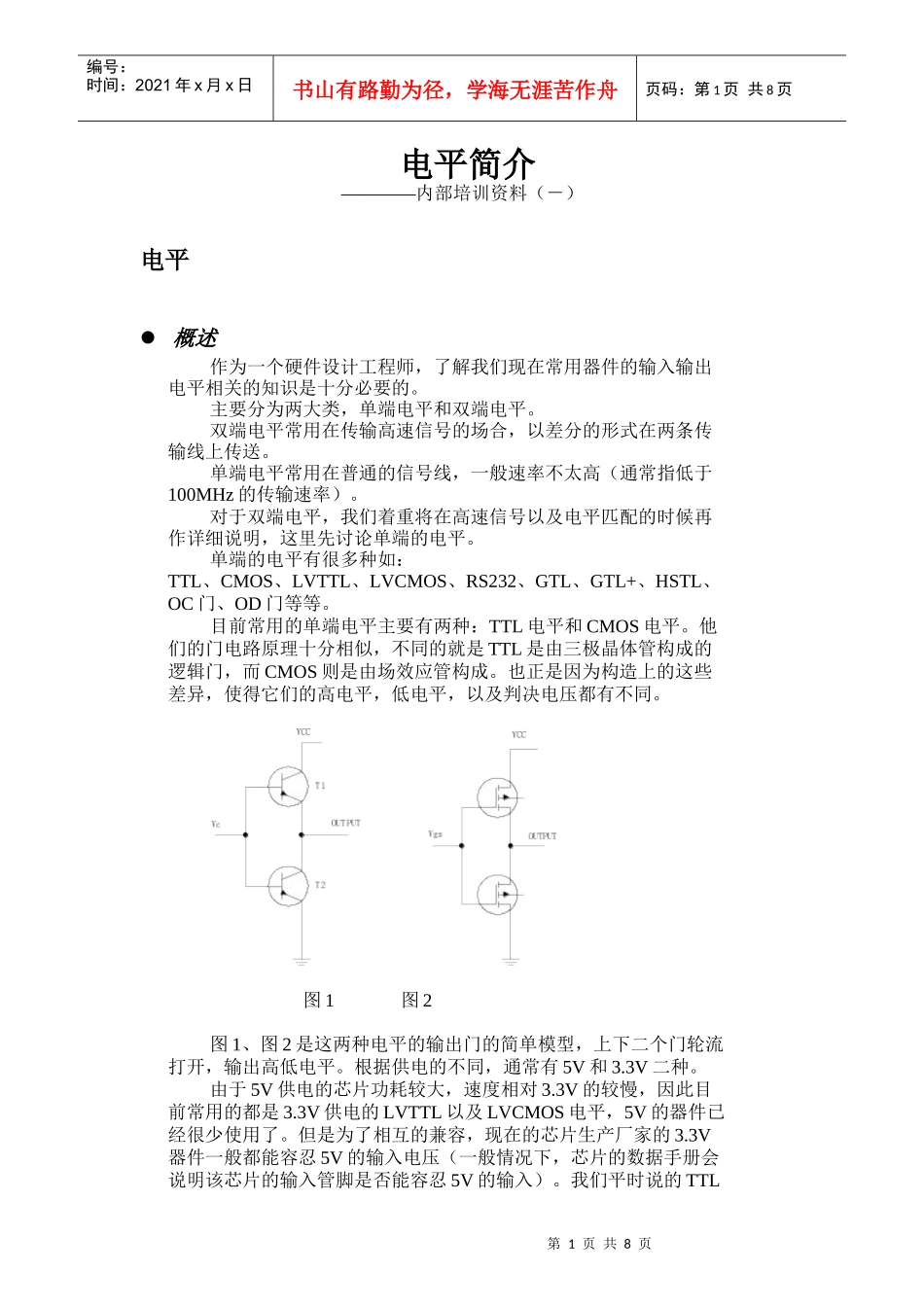

他们的门电路原理十分相似,不同的就是TTL是由三极晶体管构成的逻辑门,而CMOS则是由场效应管构成

也正是因为构造上的这些差异,使得它们的高电平,低电平,以及判决电压都有不同

图1图2图1、图2是这两种电平的输出门的简单模型,上下二个门轮流打开,输出高低电平

根据供电的不同,通常有5V和3

由于5V供电的芯片功耗较大,速度相对3

3V的较慢,因此目前常用的都是3

3V供电的LVTTL以及LVCMOS电平,5V的器件已经很少使用了

但是为了相互的兼容,现在的芯片生产厂家的3

3V器件一般都能容忍5V的输入电压(一般情况下,芯片的数据手册会说明该芯片的输入管脚是否能容忍5V的输入)

我们平时说的TTL第2页共8页第1页共8页编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第2页共8页以及CMOS电平,一般就是指3

3V供电的LVTTL和LVCMOS电平

不作特殊解释

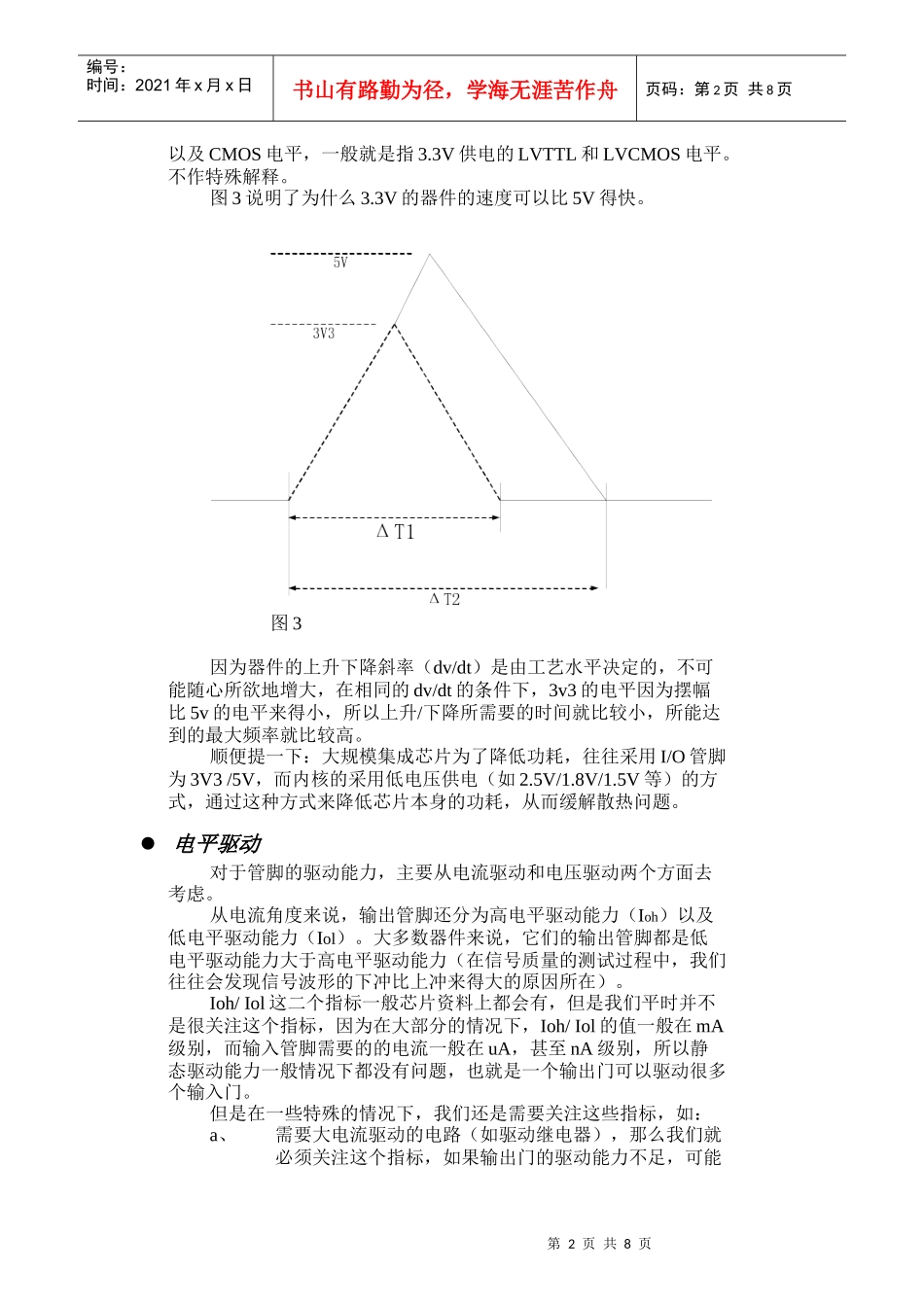

图3说明了为什么3

3V的器件的速度可以比5V得快

图3因为器件的上升下降斜率(dv/dt)是由工艺水平决定的,不可能随心所欲地增