第1页共14页编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第1页共14页《电子技术》课程设计报告《数字钟的设计》专业:班级:学号:姓名:第2页共14页第1页共14页编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第2页共14页指导教师:完成日期:2011年12月23日设计任务书一、设计题目:“数字钟的设计”二、技术要求1

设计一台能直接显示“时”、“分”、“秒”的数字钟,要求24小时为一计时周期

当电路发生走时误差时,要求电路具有校时功能

三、给定条件及元器件1

要求电路主要采用中规模集成电路CMOS或TTL2

电源电压为+5V

要求设计在数字电路实验箱上完成

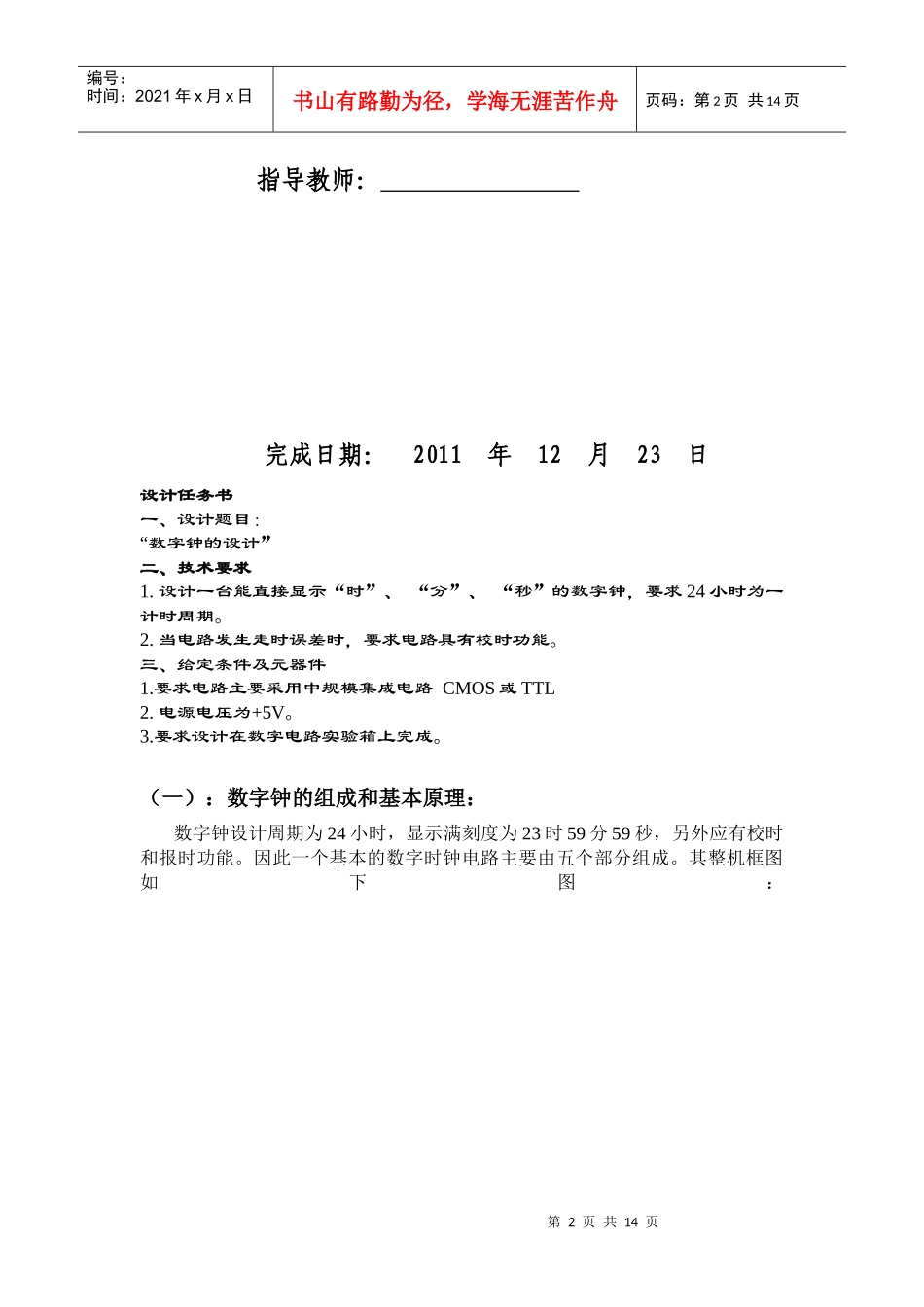

(一):数字钟的组成和基本原理:数字钟设计周期为24小时,显示满刻度为23时59分59秒,另外应有校时和报时功能

因此一个基本的数字时钟电路主要由五个部分组成

其整机框图如下图:第3页共14页第2页共14页编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第3页共14页整机框图(1):晶体振荡器晶体振荡器的作用是产生时间标准信号

数字钟的精度,主要取决于时间标准信号的频率及其稳定度

一般为保证其稳定性,一般采用石英晶体振荡器经过分频得到这一信号

选取晶振频率为32768Hz,采用十四级二进制计数器CD4060分频后,得到2Hz的信号,再由74LS74分频获得1Hz的秒信号

CD4060简介:CD4060是十四进制串行计数器,即十四分频器,管脚图如下,它内部有十四级二分频器,即Q4—Q10,Q12—Q14,其它四脚没有引出,所以只能得到十种分频系数,最小为16,最大为256

第4页共14页第3页共14页编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第4页共14页秒信号获取电路图如下:图1

秒信号获取电路(2):计数器数字钟的秒,分信号产