隔离技术简介一、隔离的目的:完整的电路是由分离的器件通过特定的电学通路连接起来的,因此在集成电路制造中必须能够把器件隔离开来,这些器件随后还要能够互连以形成所需要的特定的电路结构

隔离不好会造成漏电、击穿低、闩锁效应等

因此隔离技术是集成电路制造中一项关键技术

二、隔离技术的要求隔离区域的面积尽量要小表面尽量平坦,台阶要小制造过程中不增加缺陷(栅氧完整性,二极管漏电)器件特性不变(短沟道效应)工艺复杂度尽量要小,并和先前以及未来的工艺兼容

三、常见的隔离工艺技术结隔离(多用在双极)局部硅氧化隔离LOCOS(全称是:LOCalOxidationofSilicon)(多用在亚微米以前的工艺)基于LOCOS的技术,如PBL(PolybufferedLOCOS)、PELOX等

沟槽隔离(trench&refill),浅沟槽隔离(STI)四、LOCOS隔离:1)LOCOS0

5微米以上的MOS工艺器件之间的场氧隔离一般采用LOCOS结构,它具有制作简单的特点,在3~0

6μm的工艺中被广泛采用,缺点是隔离区会形成鸟嘴,减小了有源区的有效长度

LOCOS结构的制作过程是利用SiN薄膜掩蔽氧化层的特点,先在器件的有源区覆盖一层SiN,接着在暴露的隔离区场区通过湿氧氧化生长一层较厚的氧化层,最后去除SiN层,形成有源区,在有源区中制作器件

LOCOS的工艺流程示意图如下:鸟嘴的尺寸可以通过增加氮化硅厚度和减少有源区氧化层厚度的方法来减小,但是这样做会增加应力,导致缺陷增加

从器件的角度分析,鸟嘴的存在具有两个重要的影响:(1)氧化层侵蚀导致器件的有效宽度减小,从而减小了晶体管的驱动电流

(2)场氧化导致场注入剂扩散到有效区域的边缘

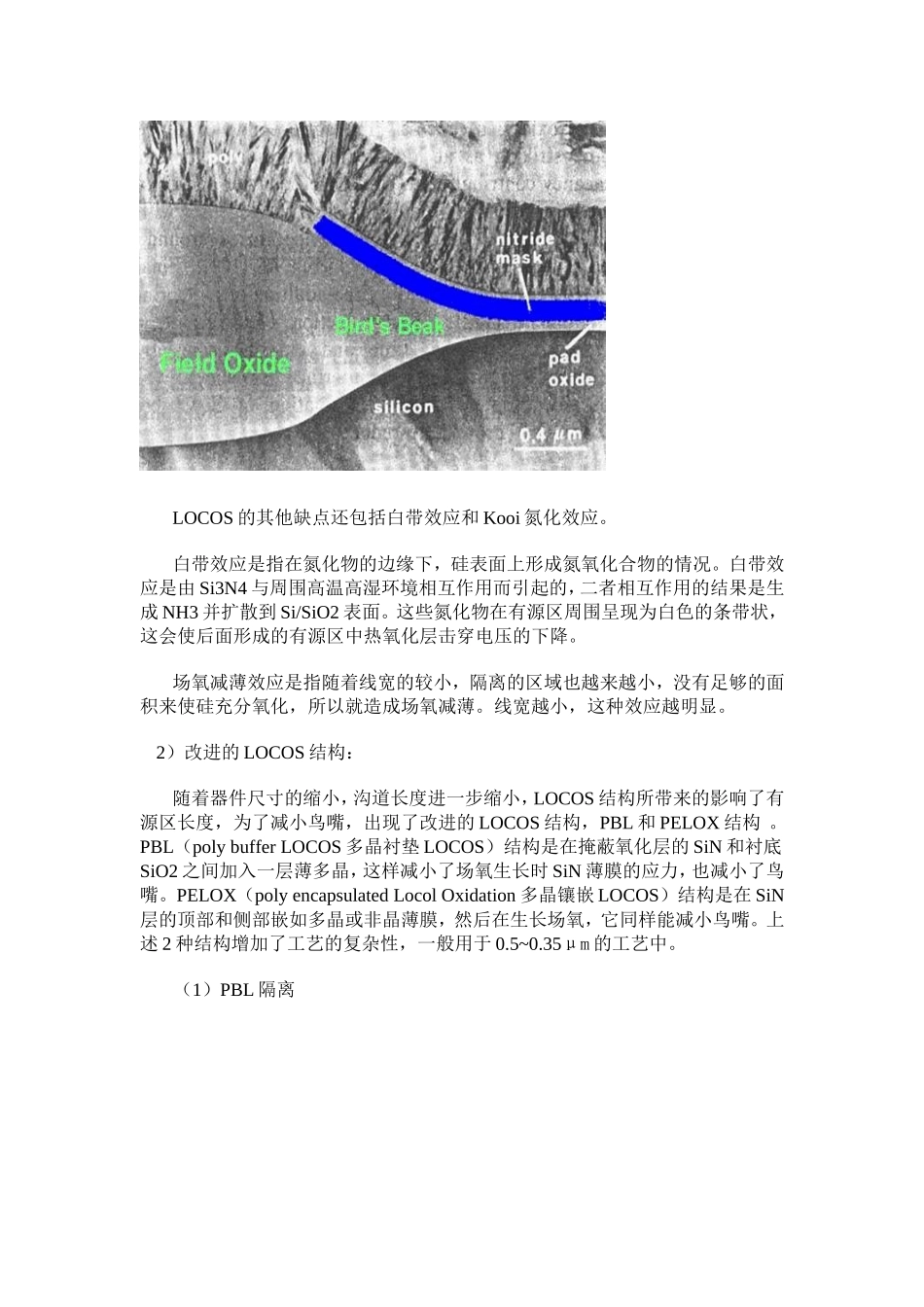

鸟嘴的SEM示意图LOCOS的其他缺点还包括白带效应和Kooi氮化效应

白带效应是指在氮化物的边缘下,硅表面上形成氮氧化合物的情况

白带效应是由Si3N4与周围