实验任务和要求

设计方案的选择

电路主要元器件介绍

电路焊接及调试

仪器仪表清单

2一、实验目的:本课程为电子、通信类专业的独立实践课,该课程设计建立在电路基础低频与高频电子线路等课程的基础上,主要让学生加深对高频电子线路理论知识的掌握,使学生能把所学的只是系统地、高效地贯穿到实践中来,避免理论与实践的脱离,同时提高学生的动手能力,并在实践中不断完善理论基础,有助于培养学生综合能力

二、实验任务和要求:2

1任务:根据数电模电知识,设计一个具有较高精度的9为数显定时器

具有数码管显示9秒的定时功能;2

定时器为9秒递减定时;3

数显定时器的记数频率可调;三、设计方案的选择:3

1方案一:它是由555电路组成的多谐振荡器构成实际脉冲发生器,一只可预置数二进制同步可逆计数器74LS193组成的脉冲计数器,译码和显示驱动器4511组成,它将输出的BCD码译码后通过数码器显示出来

R1220R210kR4DC7Q3GND1VCC8TR2TH6CV5U1555C10

01ufD015Q03D11Q12D210Q26D39Q37UP5TCU12DN4TCD13PL11MR14U274LS193A7B1C2D6LT3BI4LE/STB5QA13QB12QC11QD10QE9QF15QG14U374HC4511R3220R4220R5220R6220R7220R8220R91kC31uFD2DIODED1DIODER1010kRV11k+12v33

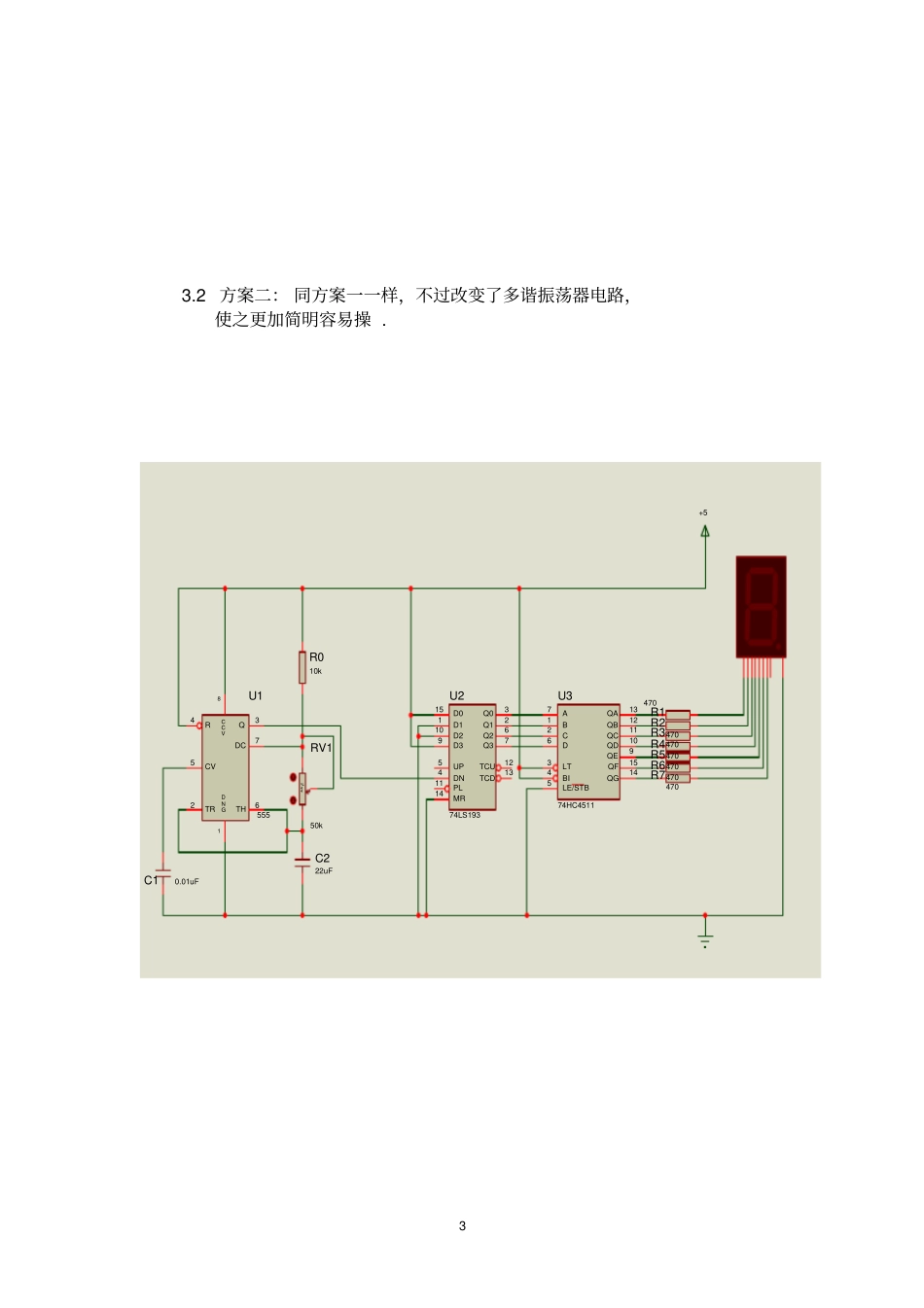

2方案二:同方案一一样,不过改变了多谐振荡器电路,使之更加简明容易操

R1470R010kR4DC7Q3GND1VCC8TR2TH6CV5U1555C10

01uFC222uFD015Q03D11Q12D210Q26D3