北京邮电大学数字电路与逻辑设计实验学院:班级:姓名:学号:班内序号:实验一一、实验名称QuartusII原理图输出法设计(一)半加器二、实验任务要求用逻辑门设计实现一个半加器,仿真验证其功能,并生成新的半加器图形模块单元

三、设计思路和过程◎设计思路半加器电路是指对两个输入数据位进行加法,输出一个结果位和进位,不产生进位输入的加法器电路,是实现两个一位二进制数的加法运算电路

数据输入:被加数AI、加数BI数据输出:半加和SO、进位CO◎设计过程(1)列出真值表输入输出AIBISOCO0000011010101101*表中两个输入是加数AI和BI,输出有一个是和SO,另一个是进位CO

(2)根据真值表写出输出逻辑表达式该电路有两个输出端,属于多输出组合数字电路,电路的逻辑表达式如下:,

所以,可以用一个两输入异或门和一个两输入与门实现

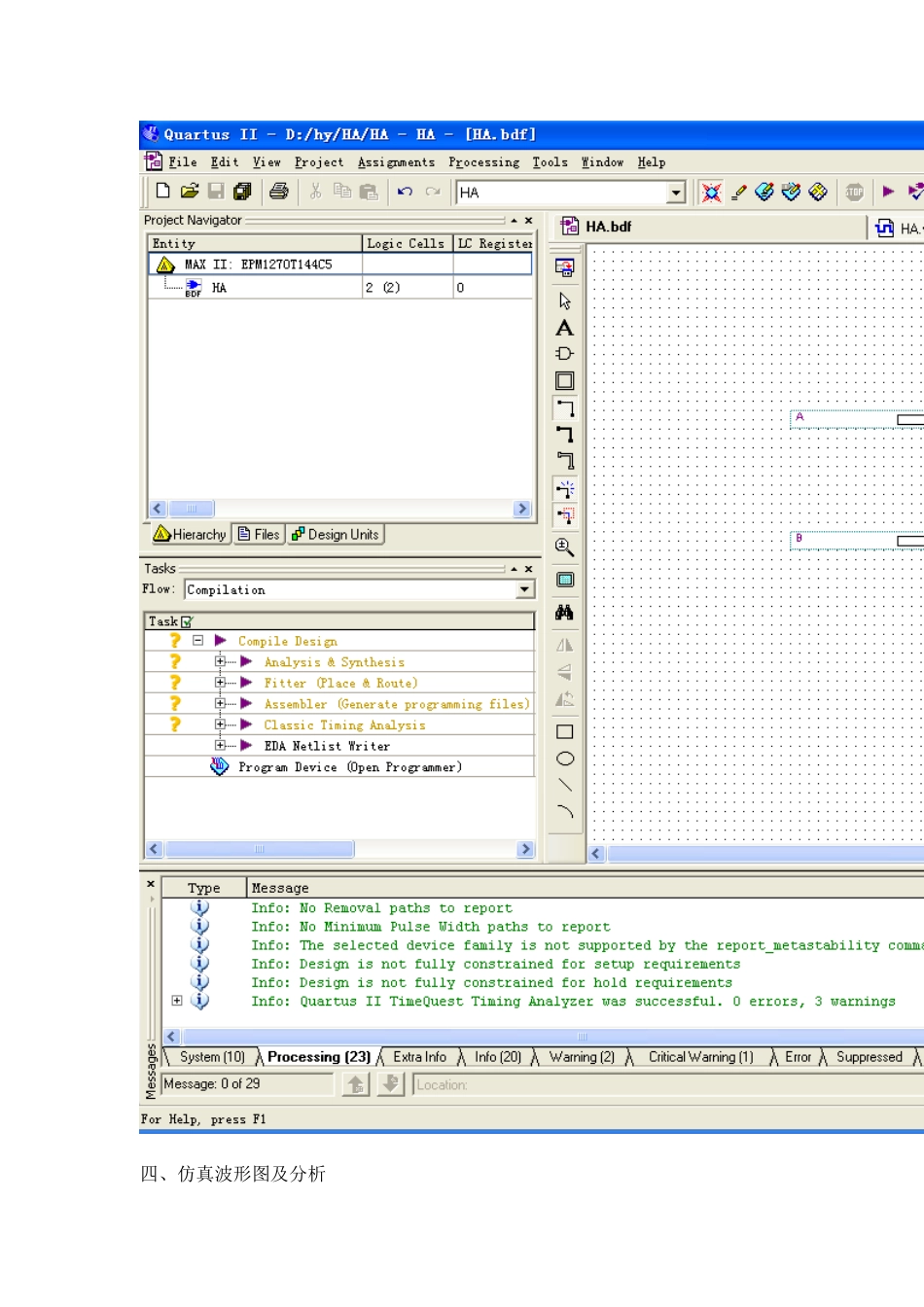

◎实验原理图四、仿真波形图及分析根据仿真波形对比半加器真值表,可以确定电路实现了半加器的功能

但我们也可以发现输出SO出现了静态功能冒险,要消除该冒险可以加入相应的选通脉冲

(二)全加器二、实验任务要求用实验内容1中生成的半加器模块和逻辑门设计实现一个全加器,仿真验证其功能,并下载到实验板测试,要求用拨码开关设定输入信号,发光二极管显示输出信号

三、设计思路和过程◎设计思路全加器与半加器的区别在于全加器有一个低进位CI,从外部特性来看,它是一个三输入两输出的器件

◎设计过程(1)全加器的真值表如下输入输出AIBICISOCO0000000110010100110110010101011100111111*其中AI为被加数,BI为加数,CI为相邻低位来的进位数

输出本位和为SO,向相邻高位进位数为CO

(2)根据真值表写出逻辑表达式:,根据逻辑表达式,可以知道只要在半加器的基础上再加入一个异或门、一个两输入与门和两输入或门即可实现全加器